目录

- 1 基本逻辑门电路测试

- 1.0 仿真激励文件testbench

- 1.1 测试与非门逻辑功能

- 1.2 测试或非门逻辑功能

- 1.3 测试异或门逻辑功能

- 1.4 测试同或门逻辑功能

1 基本逻辑门电路测试

1.0 仿真激励文件testbench

以下测试使用的testbench如下:

`timescale 1ns / 1psmodule tb_Lab1_test();logic A,B;logic C;parameter t = 100ns;initial beginA = 1'b0; B = 1'b0;#t A = 1'b0; B = 1'b1;#t A = 1'b1; B = 1'b0; #t A = 1'b1; B = 1'b1;end// 根据测试需求选择Lab1_nand tb_Lab1_test(.A(A),.B(B),.C(C));// Lab1_nor tb_Lab1_test(.A(A),.B(B),.C(C));// Lab1_xor tb_Lab1_test(.A(A),.B(B),.C(C));// Lab1_xnor tb_Lab1_test(.A(A),.B(B),.C(C));endmodule

1.1 测试与非门逻辑功能

- 编写与非门电路设计文件

module Lab1_nand(input logic A,B,output C);//逻辑门表达式如下assign C = ~ (A & B);//也可以使用SystemVerilog内置门级原语 nand g1(C,A,B);实现,在实验一中不推荐endmodule

生成电路图如下:

-

编写

testbench文件. 点击跳转 -

测试并验证正确性.

- 功能验证:只有所有输入是高电平时,输出才是低电平;否则输出高电平.

| A | B | C |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

1.2 测试或非门逻辑功能

- 编写与非门电路设计文件

module Lab1_nor(input logic A,B,output C);//逻辑门表达式如下assign C = ~ (A | B);//也可以使用SystemVerilog内置门级原语 nor g(C,A,B);实现,在实验一中不推荐endmodule

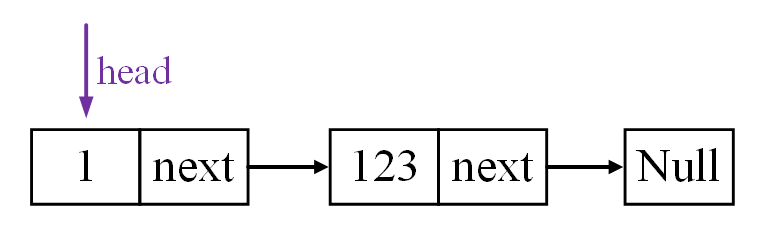

生成电路图如下:

-

编写

testbench文件. 点击跳转 -

测试并验证正确性.

- 功能验证:只有当两个输入A和B为低电平时,输出为高电平;否则输出低电平;

A B C 0 0 1 0 1 0 1 0 0 1 1 0

1.3 测试异或门逻辑功能

-

编写与非门电路设计文件

module Lab1_xor(input logic A,B,output C );//逻辑门表达式如下 assign C = A ^ B;//也可以使用SystemVerilog内置门级原语 xor g(C,A,B);实现,在实验一中不推荐endmodule生成电路图如下:

-

编写

testbench文件. 点击跳转 -

测试并验证正确性.

- 功能验证:若两个输入的电平相异,则输出为高电平;否则输出低电平.

A B C 0 0 0 0 1 1 1 0 1 1 1 0

1.4 测试同或门逻辑功能

-

编写与非门电路设计文件

module Lab1_xnor(input logic A,B, output C );assign C = ~ (A ^ B); endmodule生成电路图如下:

-

编写

testbench文件. 点击跳转 -

测试并验证正确性.

- 功能验证:当两个输入相同时,输出高电平;否则输出低电平.

A B C 0 0 1 0 1 0 1 0 0 1 1 1