文章目录

- NMOS

- PMOS

- CMOS (Complementary Metal Oxide Semiconductor)

- NAND(与非门)

- NAND layout

- NOR(或非门)

- latch up(闩锁效应)

- Channel Length vs Gate Length

NMOS

-

如果硅区域中掺杂了具有五价电子(元素周期表中的第V族)的离子,那么就会有一个额外的电子被释放到半导体中,因此电荷总体为负(N 型)

-

NMOS is built on a p-type substrate with n-type source and drain diffused on it. In NMOS, the majority of carriers are electrons. When a high voltage is applied to the gate, the NMOS will conduct. Similarly, when a low voltage is applied to the gate, NMOS will not conduct. NMOS is considered to be faster than PMOS, since the carriers in NMOS, which are electrons, travel twice as fast as the holes.

-

最简单的 MOSFET 结构由一个衬底(可以是P型或者N型)和两个与 体区极性相反的硅区域组成,它们构成了漏极和源极。MOSFET可以构建为具有P型衬底和N型漏极与源极区域,这意味着,要使电流从漏极流向源极,沟道也必须为N型。这种结构被称为N沟道MOSFET,或NMOS晶体管

PMOS

-

在价带中具有三个电子的元素将缺少一个电子,这相当于贡献了一个空穴,意味着总电荷为正(P型)

-

P- channel MOSFET consists of P-type Source and Drain diffused on an N-type substrate. The majority of carriers are holes. When a high voltage is applied to the gate, the PMOS will not conduct. When a low voltage is applied to the gate, the PMOS will conduct. The PMOS devices are more immune to noise than NMOS devices.

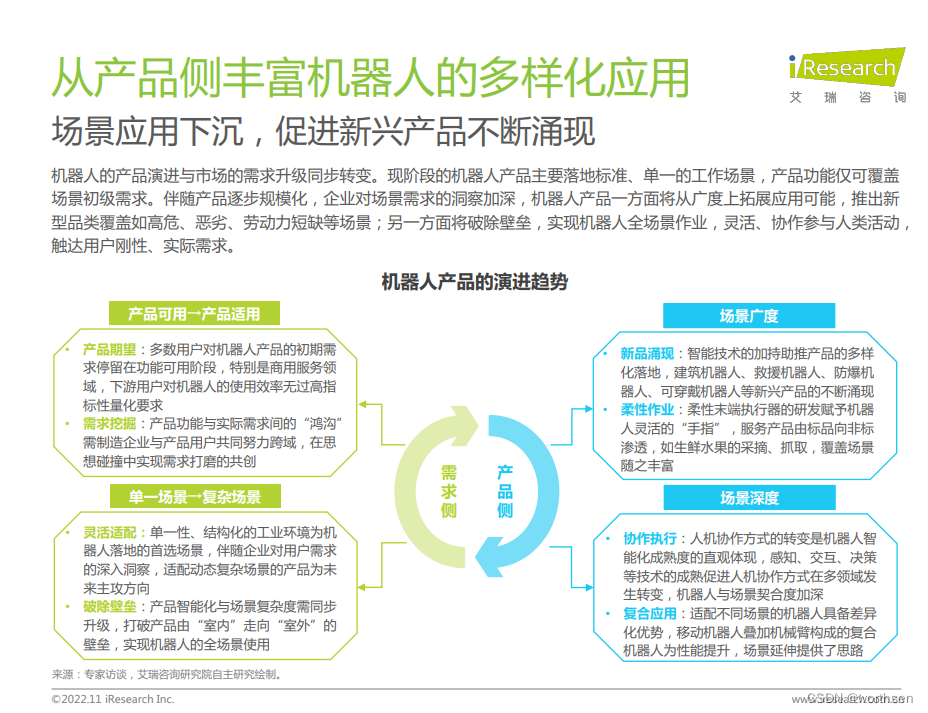

CMOS (Complementary Metal Oxide Semiconductor)

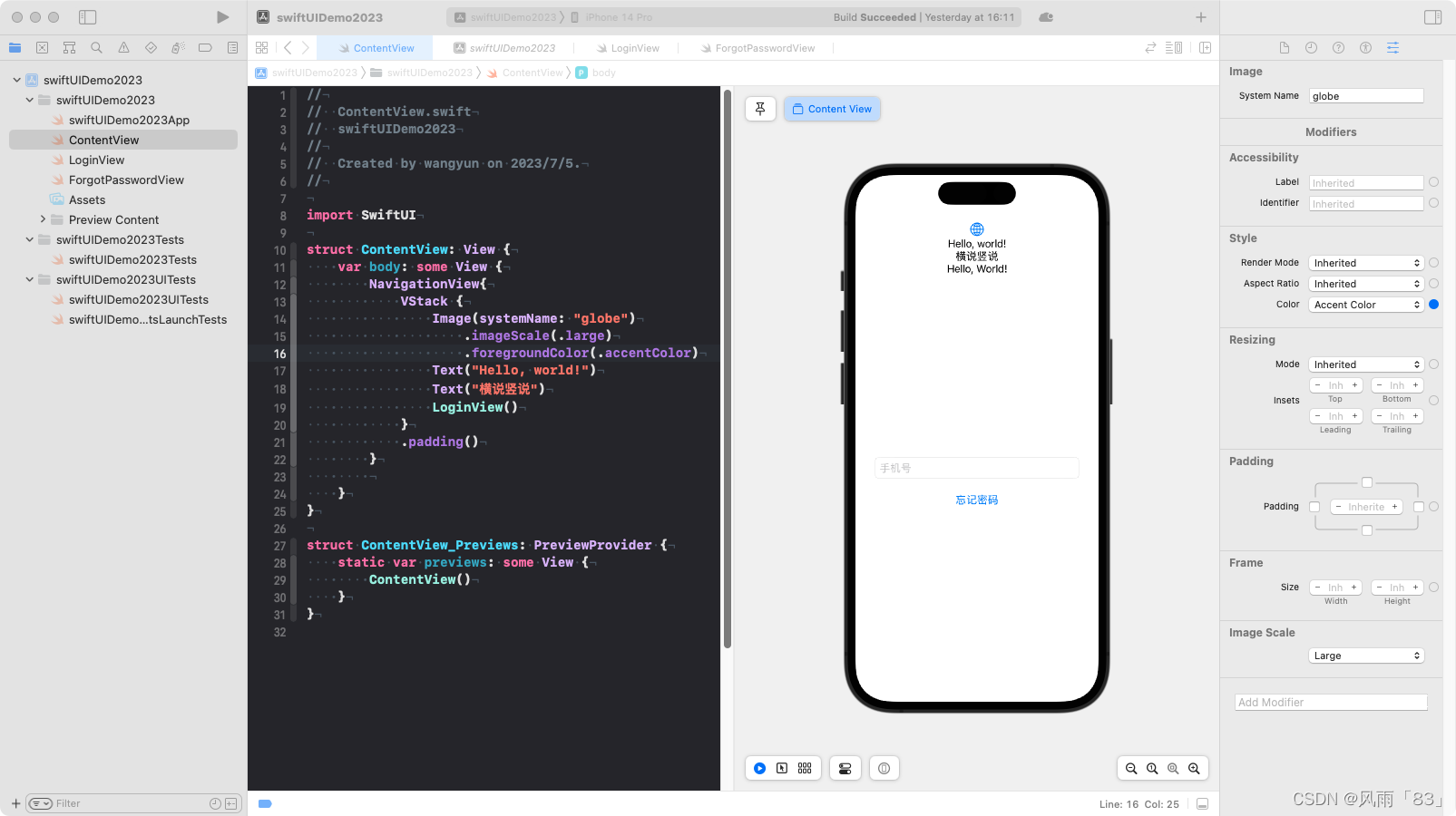

The inverter circuit as shown in the figure. It consists of PMOS and NMOS FET. The input A serves as the gate voltage for both transistors.

The NMOS transistor has input from Vss (ground) and the PMOS transistor has input from Vdd. The terminal Q is output.

-

When a high voltage (Vss/~Vdd) is given at input terminal (A) of the inverter, the PMOS becomes an open circuit, and NMOS switched OFF so the output will be pulled down to Vss.

-

When a low-level voltage (logic 0) applied to the inverter, the NMOS switched OFF and PMOS switched ON. So the output becomes Vdd or the circuit is pulled up to Vdd.

The N device is manufactured on a P-type substrate while the P device is manufactured in an N-type well (n-well).

A P-type substrate “tap” is connected to VSS and an N-type n-well tap is connected to VDD to prevent latchup.

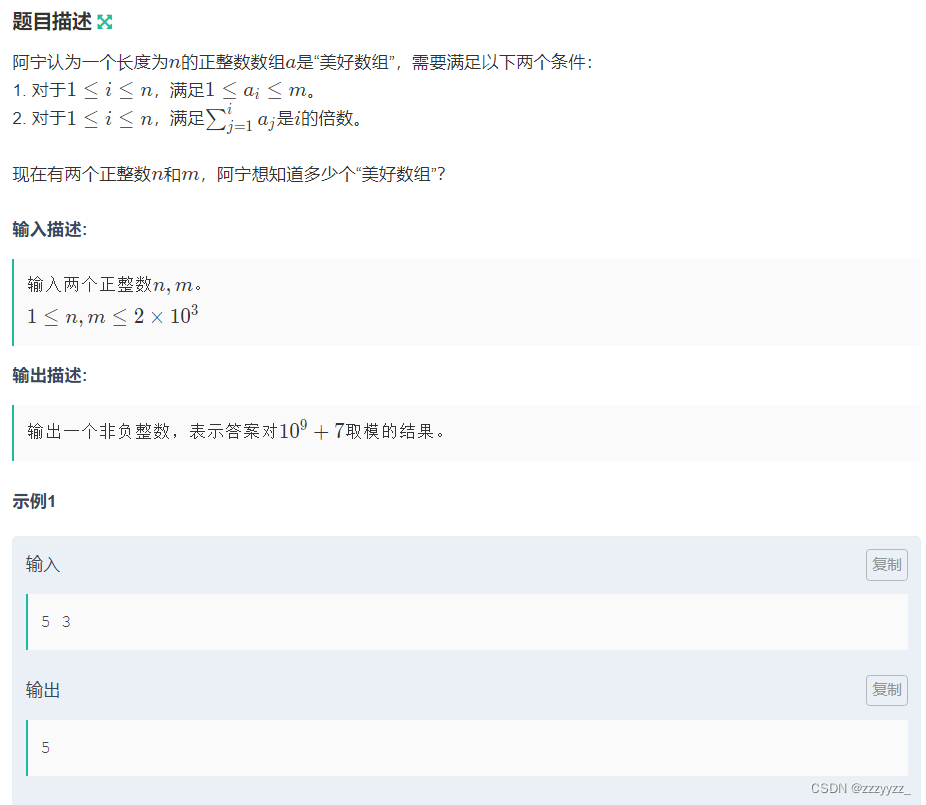

NAND(与非门)

-

两输入NAND,两个pmos并联,两个nmos串联

-

n输入的NAND就是n个pmos并联,n个nmos串联

-

If either input A or B is logic 0 (AB=00、01、10), at least one of the NMOS transistors will be OFF, breaking the path from OUTPUT to Ground.

(NMOS至少不导通一个) -

If both inputs are high, both of the nMOS transistors will be ON and both of the pMOS transistors will be OFF. Hence, the output will be logic low. The truth table of the NAND logic gate given in the below table.

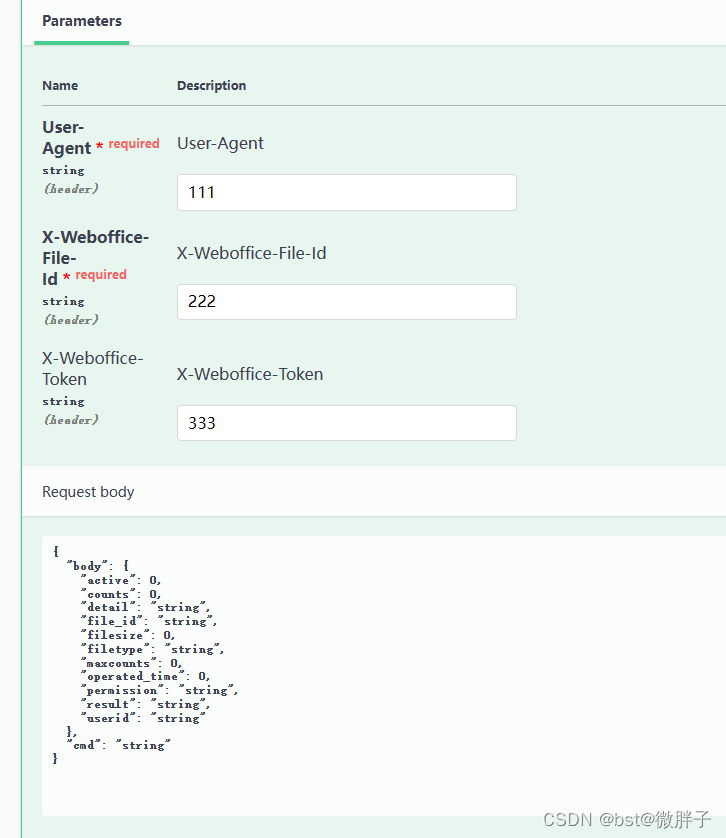

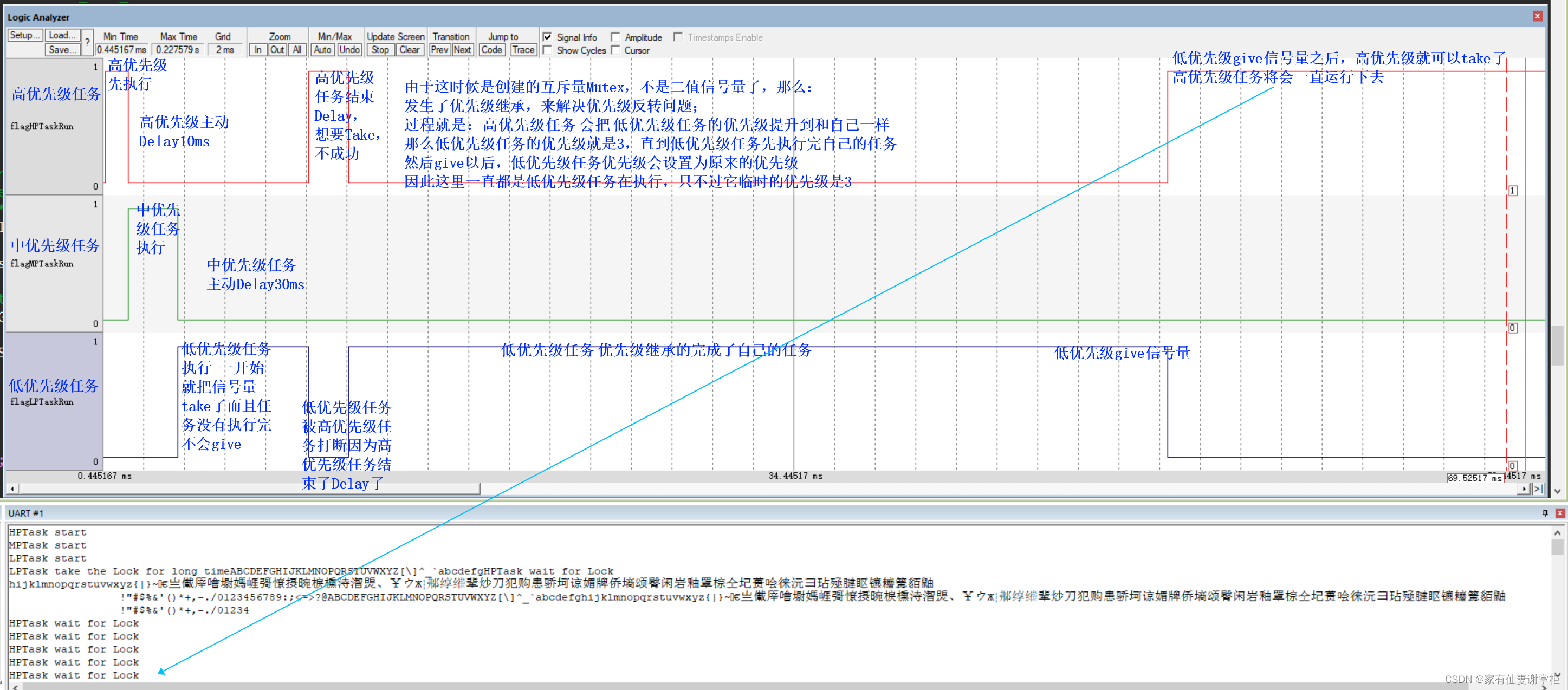

NAND layout

#pic_centerAt the top of the standard cell, there is VDD rail and bottom there is a VSS rail. Both the Power rails are drawn in the Metal-1 layer. In between the VDD rail and VSS rail there are three main regions, a nwell region, a gap of nwell and pwell and pwell region. nwell region is near to the VDD rail and pwell region is near the VSS rail. pMOS transistors are build inside the nwell, so all the pMOS transistors are in the top half of the cell and similarly, all nMOS are in the bottom half of the standard cell.

The physical layout of a NAND circuit. The larger regions of N-type diffusion and P-type diffusion are part of the transistors. The two smaller regions on the left are taps to prevent latchup.(数字后端physical cell welltap/tapcell 防止latch up)

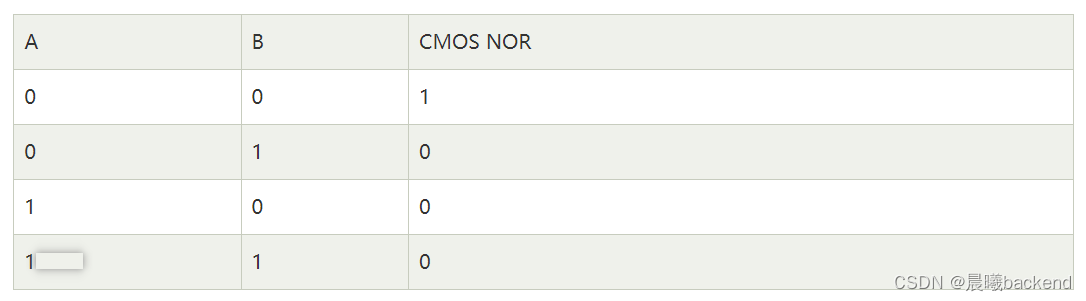

NOR(或非门)

- When both the input A and B are 0, NMOS NOR will remain OFF, and PMOS NAND will conduct. It means that transistors T1 and T2 will be OFF, while T3 and T4 will conduct. Thus, the output will be logic 1 when the voltage VDD reaches through the conduction of transistors T3 and T4.

- If either input A or B is logic 1 (AB=11、01、10), at least one of the PMOS transistors will be OFF, breaking the path from OUTPUT to Vdd.

(PMOS至少不导通一个)

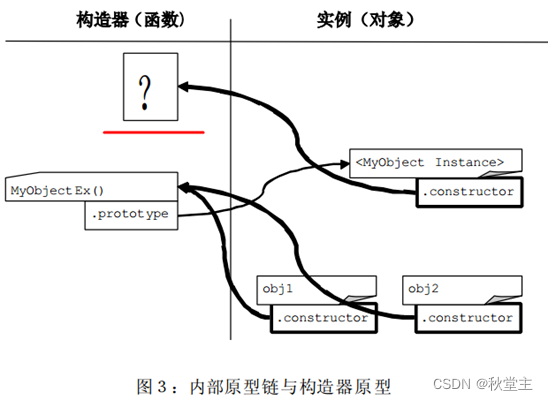

latch up(闩锁效应)

-

In the simplest way, the latch-up issue can be defined as a formation of a direct path from VDD to GND terminal in the design, which will cause a huge current flow between the power and ground terminal.

-

Once the latch-up occurred in CMOS design, lots of current start flowing directly from VDD to GND and will cause the failure of chip. So we must protect our chip from latch-up. (add physical cell welltap/tapcell)

-

Inside a CMOS (Complementary Metal Oxide Semiconductor) circuit, two parasitic BJT (Bipolar Junction Transistors) get formed and connected in such a way that these BJT form a PNPN device or SCR (Silicon-Controlled Rectifier) or Thyristor. Formation of the PNPN device is shown in the figure below.

-

When we say that we have let’s say a 28 nm technology node.

-

It would be the GATE LENGTH! As pointed above, gate corresponds to the minimum feature size mask which is characteristic of a particular technology node!

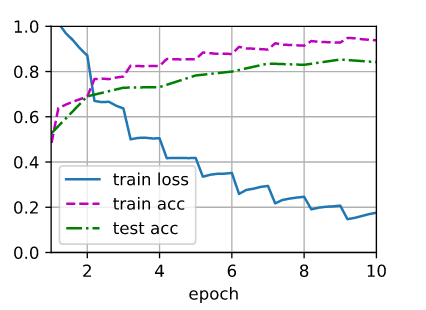

- channel length 对于漏极电流公式有影响,

channel W/L与ld成正比,沟道越短,cell delay越小