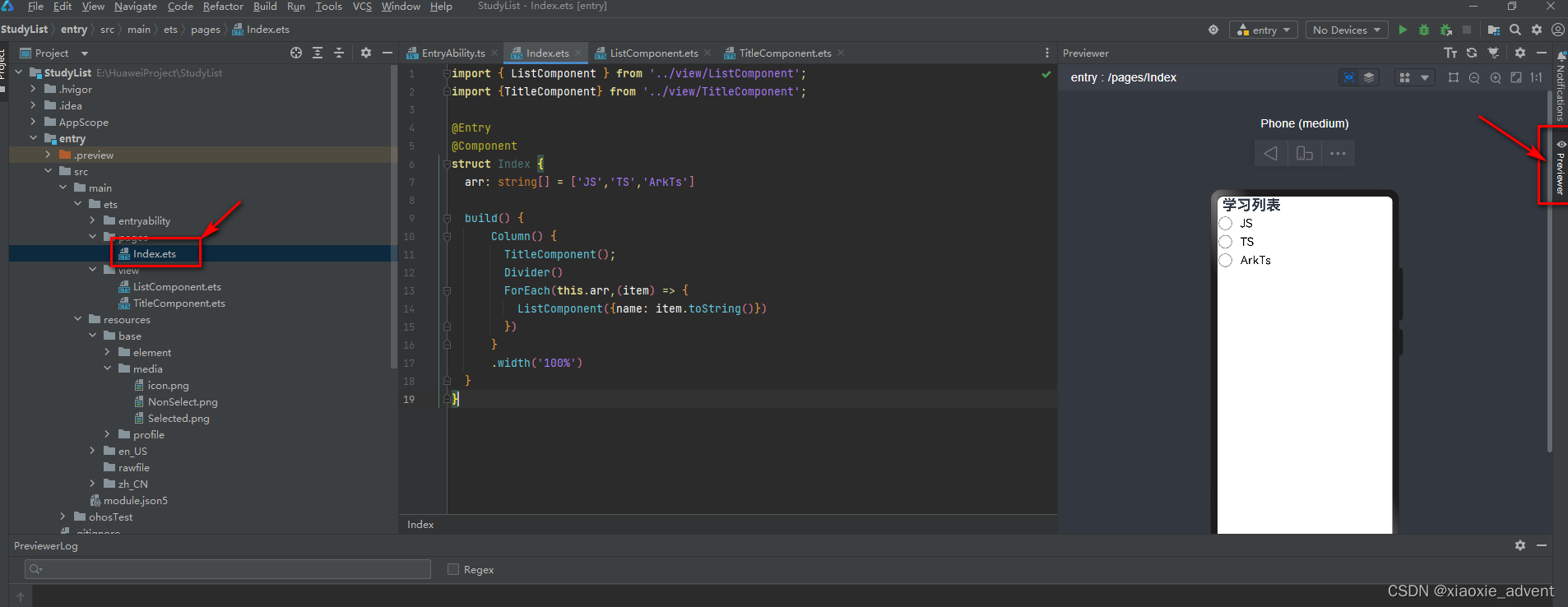

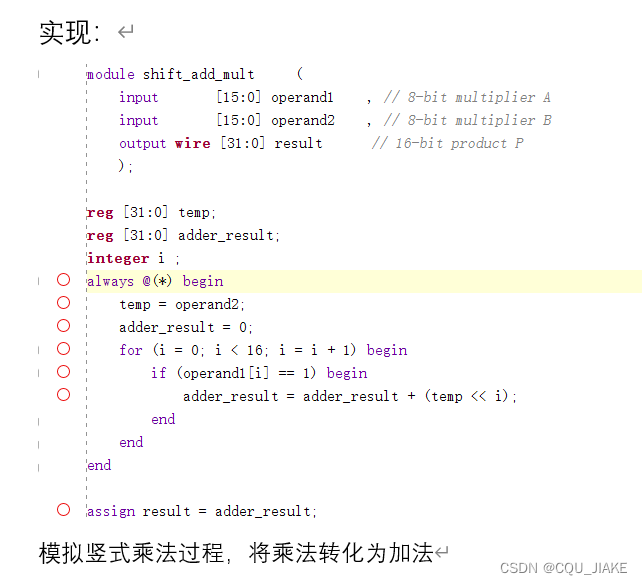

for循环乘法器

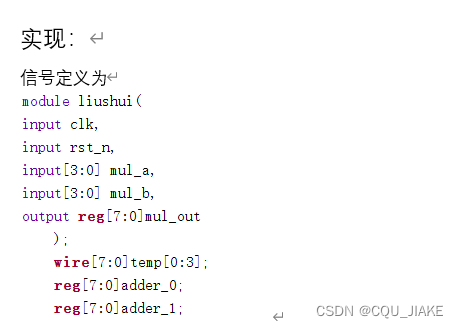

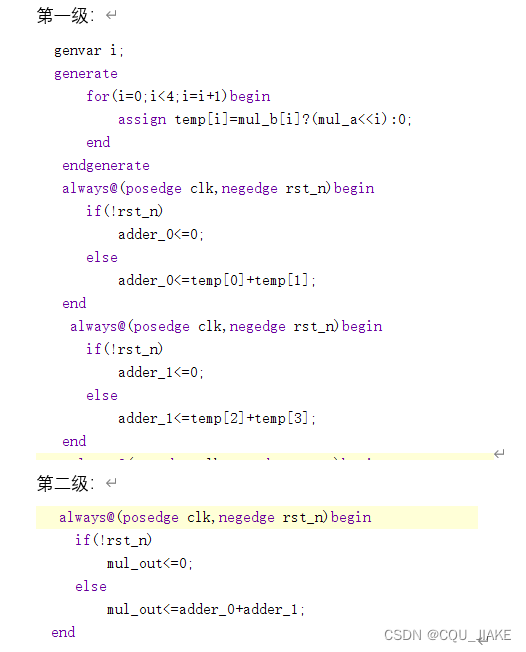

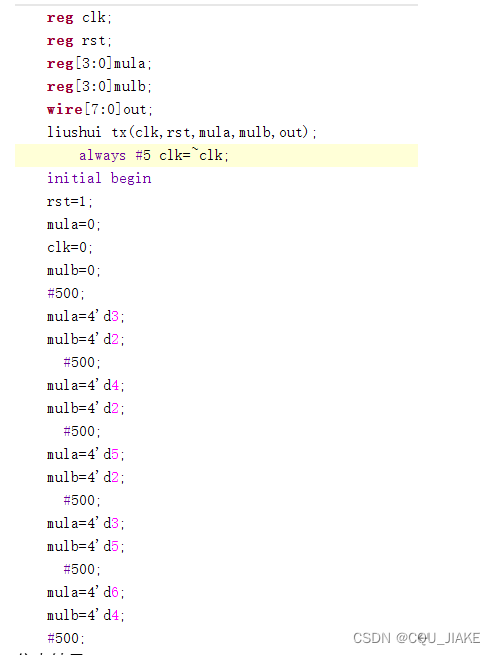

流水线乘法器

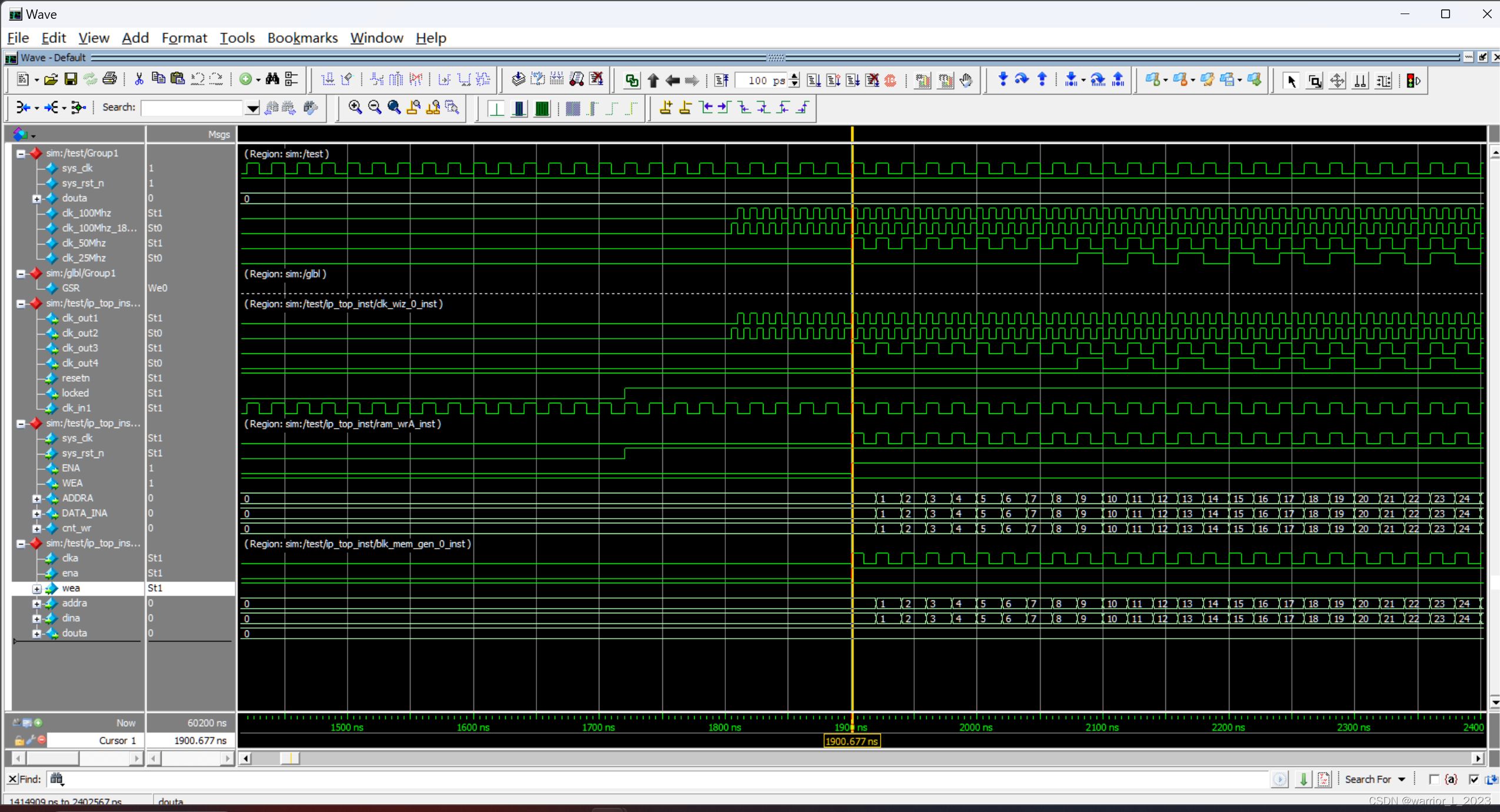

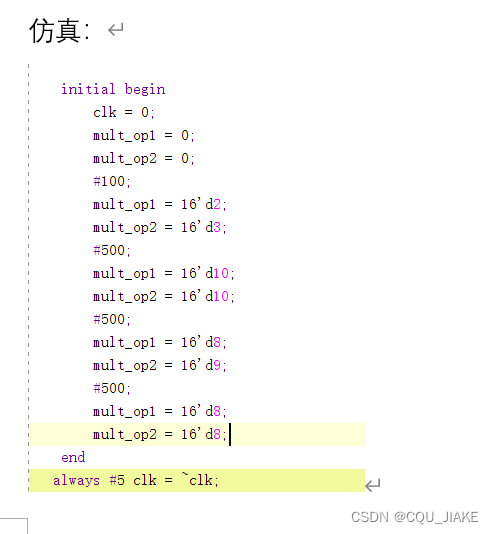

仿真的时候,注意把clk设置一个初始值

分析报告

电路图分析:

比对两种实现方式的RTL级电路图可以发现,for循环的乘法器本质为转为不断的循环累加,故最终电路长度很长,取决于循环,即累加的次数;而对于流水线乘法器,虽然本质也是累加,但是为两两累加,一级一级的累加,操作次数折半减少,形成树形结构,所以可以很好地缩短电路长度。

功率分析:

一方面是位数不同导致功率有显著差异,另一方面是实现方式不同导致的系统性功率不同。

流水线实现的乘法器较同位循环实现的乘法器,更加节省功率;而若循环实现的乘法器采用移位存储的方式,则二者(同位数下)功率差距并不大,即优化后的循环乘法器若采用移位存储的方式,那么每次循环中都不需要移动i位,而只需要在上一次循环的基础上只移动一位即可,但整体而言相比同位的流水线乘法器还有一定的系统功率差距。