在数字IC后端设计实现中,我们经常会涉及到芯片需要做Function ECO。常见的Function ECO可以分为pre mask ECO和post mask ECO两种。因此,作为一个数字IC后端工程师,必须熟练掌握这两种Function ECO的实现流程及其实现技巧。

两者的区别在于,pre mask ECO的晶体管和布线层都还没有开始做出mask,此时可以往netlist里面添加cell。而post mask ECO的晶体管层已经开始进行加工了,但是布线层还没有加工,还能修改,可以通过ECO改变各种已有cell的连线关系,但是不能添加新的cell,有一定局限。

换句话说,从freeze到tapeout之间的ECO叫pre mask ECO;

tapeout之后的ECO叫做post mask ECO。这里包含以下几种情况:

1)芯片已经tapeout base layer后的ECO

2)芯片已经wafer out的ECO

Pre mask ECO:

Pre mask ECO比Post mask ECO要灵活得多。在tapeout之前,如果发现有任何需要修改的地方,都可以用这种方法。它可以改成百上千个单元。该操作主要是针对静态时序分析和后仿真中出现的问题,对电路的网表直接进行修改,待网表修改完毕之后反馈到PR工具中对标准单元的布局和连线进行小范围的改动。当然,直接对网表进行修改是存在风险的,所以之后一定要进行形式验证(formal verification),确保功能实现。

Post mask ECO:

Post mask ECO是利用预先留好的备用单元(Spare Cell或ECO Cell),做的逻辑修改。如果后期发现Timing存在问题(或者想小动Function),可以利用附近的Spare Cell或ECO Cell搭配上层金属连线来修改电路结构。比起Pre mask ECO,这种ECO受限于Spare Cell的位置,所以它的修改规模十分有限。

ECO cell和Spare cell的区别

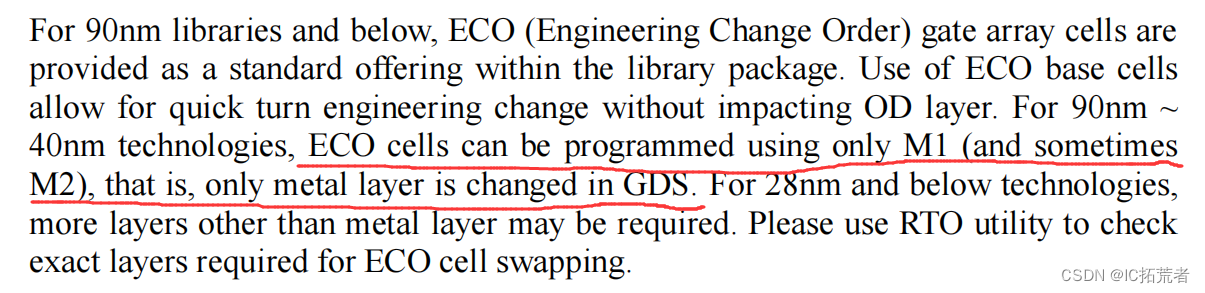

Spare cell其实就是正常的逻辑功能cell,而ECO Cell则仅仅是把相关的base layer做好了,其他都没有任何连接的cell。也就是说ECO Cell理论上是可以充当library库中常见的逻辑功能cell。

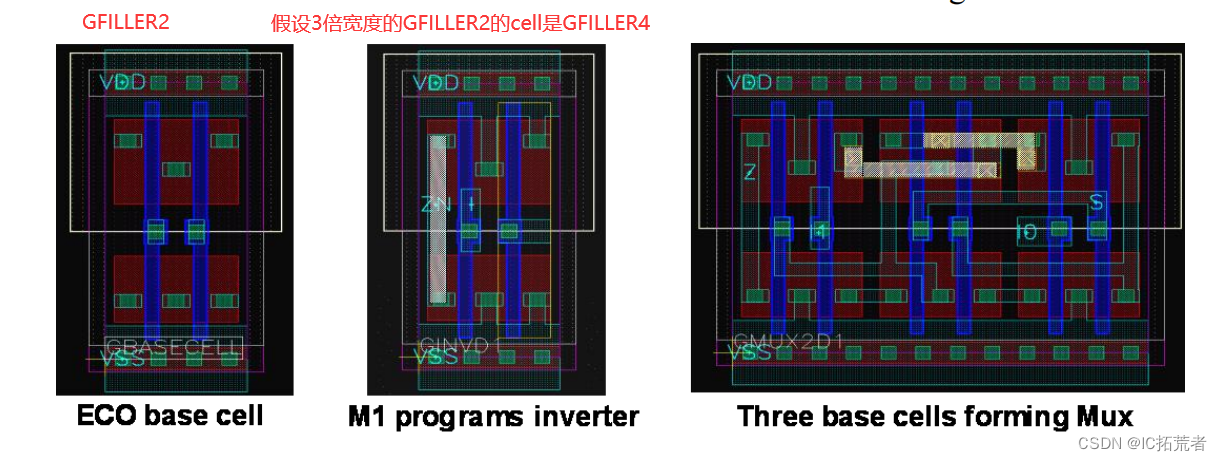

ECO cell是内部晶体管没有链接的cell, 是可以被『编程』的cell, 在做ECO 时,通常用最底层金属如M1 将ECO cell 内部的晶体管链接起来,以实现对应的逻辑功能,如:与或非、选择器、寄存器等等。

所以,Spare cell的优势明显不如ECO Cell。而且更重要的是spare cell是正常的逻辑单元,它们的input都需要接到tie cell上(不允许有任何的input floating情况)。

而且Spare Cell的逻辑功能类型还得备齐,否则需要做ECO时可能会发现没有想要的逻辑功能cell。一般spare cell都是以一系列常见逻辑功能cell堆叠在一起的一个阵列。

当然Spare cell也有一个好处,就是后期ECO时只需要动到Metal layer,而ECO cell是需要动到Contact这一层。

目标需求

做任何ECO的目的是非常明确的,希望把我们功能上的bug修复掉,而且成本越低越好,最好是不花钱。

Pre-mask ECO是不需要额外的mask成本,但Post-mask ECO则大概率是需要额外的mask成本。

比如目前芯片已经tapeout,foundary还在加工base layer,此时如果要做的ECO仅仅需要更改metal layer(因此两个ECO点很近,只需要改连接),那么是可以不花费额外的mask成本的。

【思考题】如果芯片已经tapeout,foundary已经即将完成base layer的加工,此时如果要做的Function ECO需要添加一些逻辑功能cell,是否一定会增加mask的成本?

又比如芯片已经wafer out,芯片封装测试后发现存在功能上的Bug,需要加入一些运算逻辑。此时肯定需要动到Metal layer甚至base layer。所以这时候做ECO的代价是最大的。

那此时为了最大程度减少做ECO带来的成本,在数字后端实现时就需要想办法尽量不动base layer以及少动metal layer来完成我们的Function ECO。

怎么做?

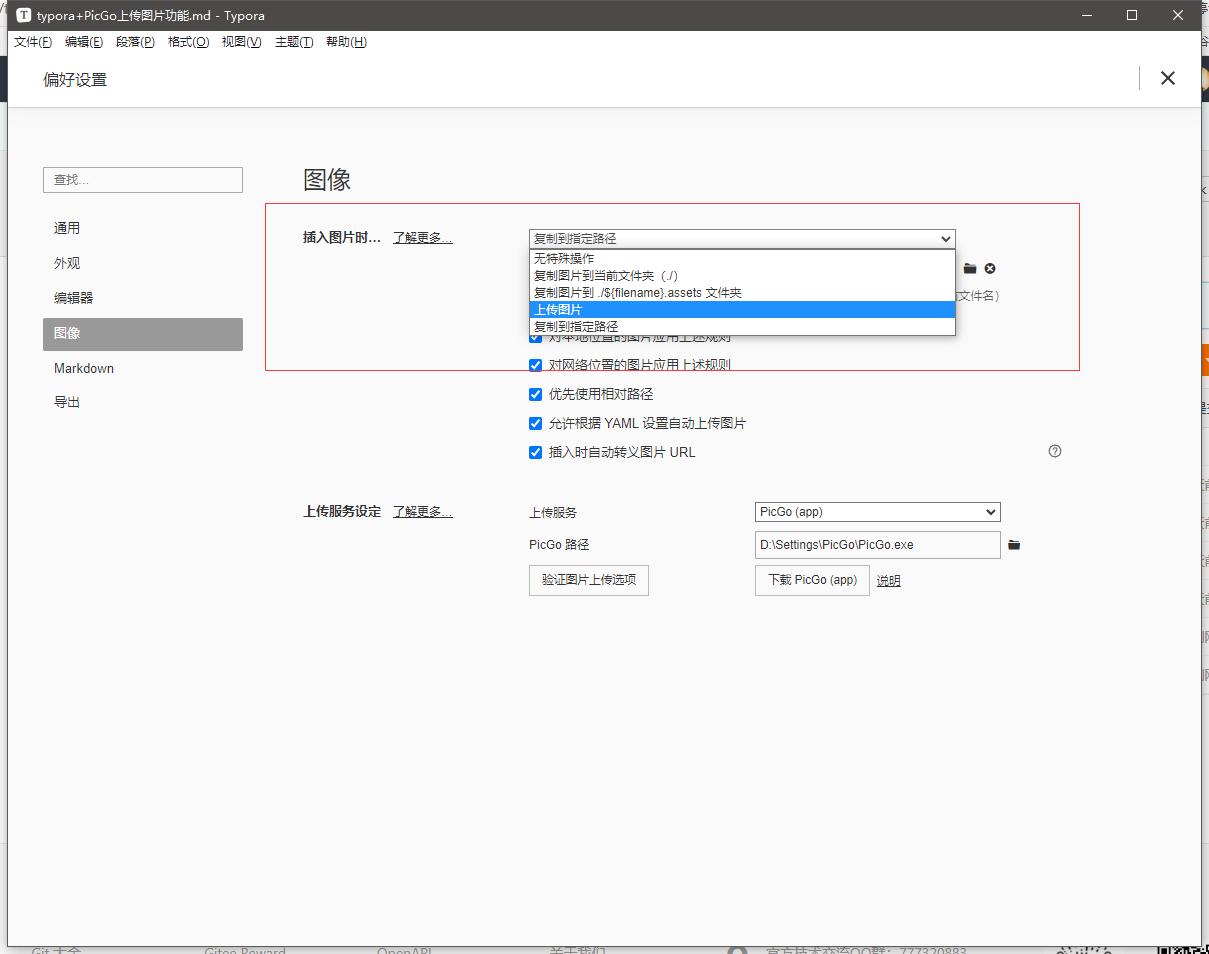

知道数字IC后端实现PR flow的同学,都知道我们在route opt结束后还有一步是chip finish。这步就是插普通Filler和ECO Filler。

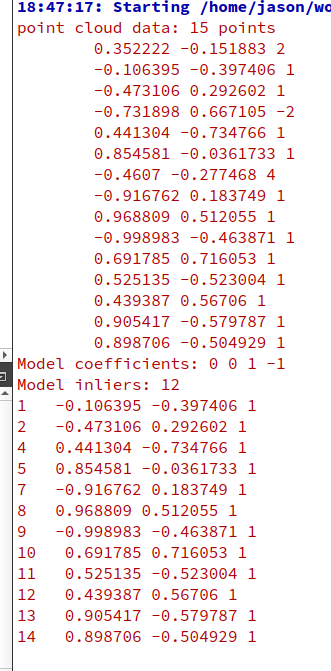

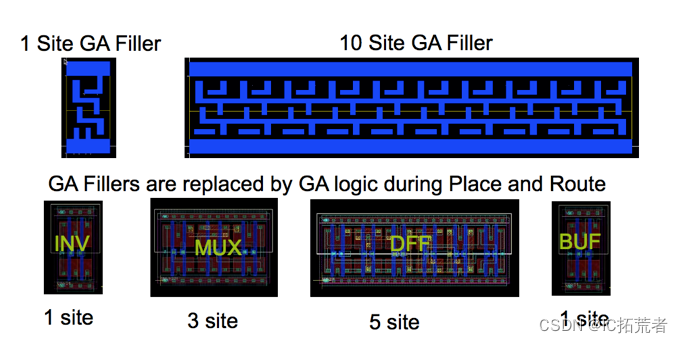

在做ECO 之前这类ECO Filler『GA array filler』被放在设计中,在做ECO 时会用GA functional cell 替换GA filler cell. GA Array filler 是physical only cell, 就是只在lef 中有定义在lib 中没有定义,只存在于DEF 中不在netlist 中。GA functional cell 才是真正有逻辑功能的cell.

在实现过程中,先用GA array Filler 占位置,有ECO进来时,需要先将GA array Filler remove 掉,再把GA functional cell放置上去,如果加入的GA functional cell宽度小于原来的GA Filler,我们还需要在剩下的空位上填上新的GA array filler。

GA cell 有多种site, 如1, 3, 5, 10. ECO 时可以根据逻辑功能,将一个GA Filler 映射成多个GA functional cell. 传统的GA cell 内部没有任何预先定义的逻辑功能,所以可以用来组合任何逻辑功能,如一个10-site 的GA filler 可以映射成:10个inverter 或5个MUX 或1个DFF。

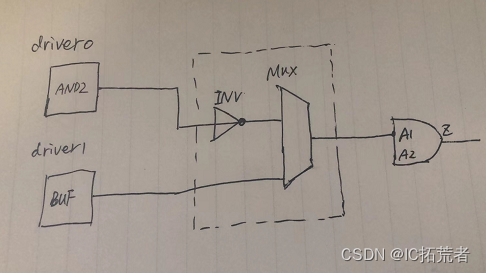

这里举一个芯片测试阶段发现的功能Bug例子。下图虚线框内为需要新增的逻辑功能cell。

ECO base cell如下图最左侧所示,对应的名字为GFILLER2。通过查看ECO库我们发现这个cell的大小刚好与GA Function CELL Inverter是同等大小。而且发现ECO功能cell Mux的大小与ECO FillerX4大小是一致的。

所以,针对这个Post Mask ECO,我们首先需要在driver0,driver1和后面那个AND2这中间找出一个GFILLER2和一个GFILLER4的ECO Filler cell,然后用GA Functional inverter和MUX进行替换。

其次,还需要将对应的逻辑连接好。这里主要涉及到以下几个逻辑连接:

1)driver0和driver1对应的net断开

2)将driver0和inverter的input端连接在一起

3)将mux的两个输入端分别连接到inverter的输出和driver1上

4)将原来load的A1 pin对应的net断开,并把它连接到mux的输出端

最后,设置绕线层次范围约束,做ecoRoute。

如果希望有个实战环境,可以参加咱们社区的IC训练营进行实战演练。

如何检查做的对不对?

比如上面那个ECO,我们设置了只能用M1-M3来绕线。完成绕线后我们肯定无法通过肉眼来看是否有使用M3以上的金属层来绕线,那么我们如何来确保工具按照我们约定的条件来做了呢?

答案是做LVL(Layout比Layout).这个工作通过calibre工具就可以完成。主要原理是通过比对ECO前后两个GDS的差别。