时序异常

关于定时例外

当逻辑的行为方式未被正确计时时,需要计时异常违约任何时候都必须使用计时异常命令来处理计时不同地(例如,对于每隔一个时钟周期仅捕获结果的逻辑设计)。

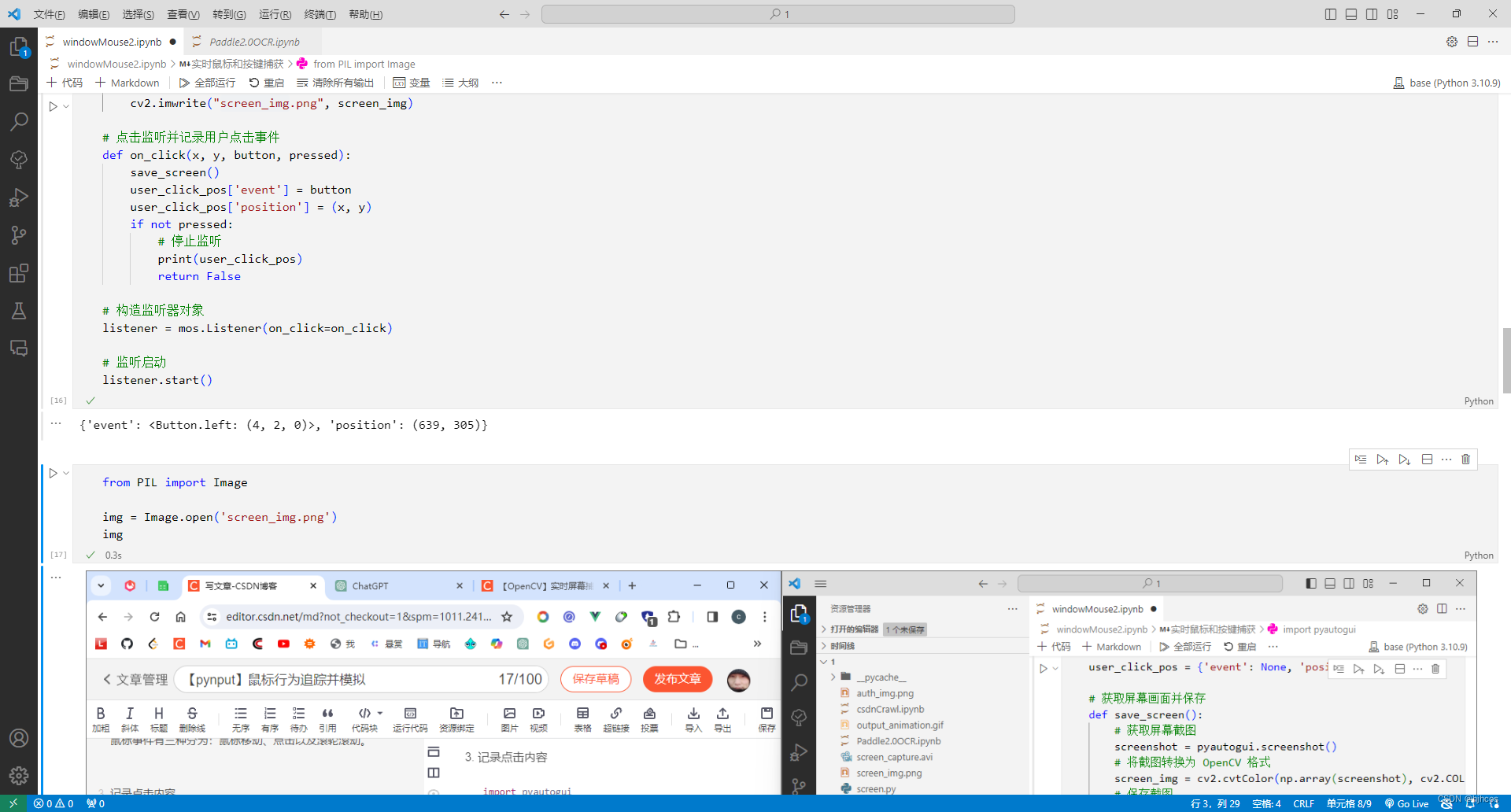

AMD Vivado™IIDE支持下表中显示的定时异常命令:

多循环路径

多循环路径约束允许您修改已确定的设置和保持关系由定时器基于设计的时钟波形来执行。默认情况下,Vivado IDE计时引擎执行单循环分析。这种分析可能过于严格,不适合某些逻辑路径。最常见的例子是需要一个以上时钟周期的逻辑路径要在端点处稳定的数据。如果路径起点和终点的控制电路允许它,AMD建议您使用多周期路径约束来放宽设置要求。保留要求可能仍然保持原始关系,这取决于您的意图。这帮助定时驱动算法专注于其他要求更严格的路径这是具有挑战性的。它还可以帮助减少运行时间。

设置路径乘法器和时钟边沿

set_multycle_path命令用于修改路径要求乘数(用于设置分析、保持分析或两者)。

set_multipcycle_path语法

带有基本选项的set_multipcycle_path命令的语法为:

您必须指定<path_multiplier>。计时器使用的默认值为:

•1个用于设置分析(或恢复)

•0用于保留分析(或删除)

保留关系与设置关系相关联。使用以下公式检索大多数常见情况下的保持周期数:保持周期=<设置路径乘数>-1-<保持路径乘数>

•默认情况下,设置路径乘数是相对于目标时钟定义的。到修改关于源时钟的设置要求,使用-start选项。

•类似地,保持路径乘法器是相对于源时钟定义的。要修改保持目标时钟的要求,使用-end选项。

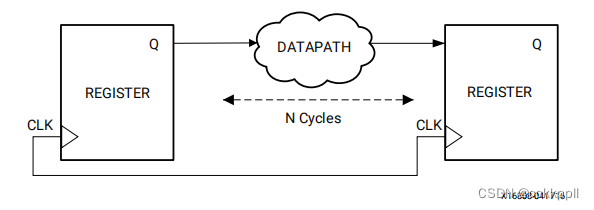

下表总结了活动启动和捕获边缘如何受到-开始和结束选项。

以下部分介绍了常见的多循环路径约束场景,并说明了设置和保持乘数以及开始和结束选项对时序路径的影响要求.

单时钟域中的多循环

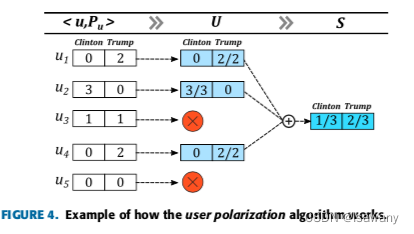

在同一时钟域内或具有的两个时钟之间定义的多周期约束相同的波形(无相移)以相同的方式工作。如下图所示。

由静态时序分析(STA)解析的默认设置和挂起关系

工具如下图所示。

设置和保持时间要求为:

•设置检查

t数据路径(最大值)<TCLK(t=周期)-t设置

•保持检查

t数据路径(min)>TCLK(t=0)+t旧

保持保持的同时放松设置

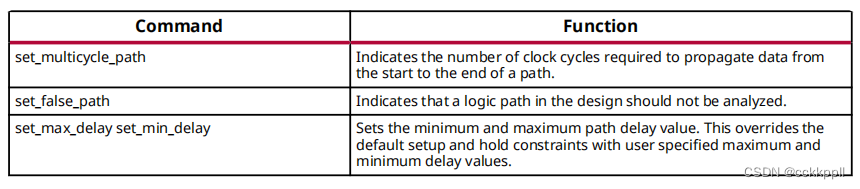

下图显示了每两个周期启用一次的两个触发器之间的路径。是的可以安全地在此路径上定义多循环路径约束,以指示目标时钟未激活,只有目标时钟的第二个边缘将捕获新数据。

以下约束将建立新的设置关系:

Vivado Design Suite用户指南中的此链接:设计分析和闭合技术(UG906)描述了保持关系是如何从设置关系导出的。修改时设置关系、保留关系也会进行修改,以遵循设置中的更改发射和捕获边缘。

在与图61相同的示例中,将设置检查移动到第二个捕获边缘后保持检查自动移动到第一个捕获边缘(即设置检查)。下图显示了仅当设置路径乘数已经用多循环路径约束来定义。

此路径不需要将数据保存在data0_reg中一个周期即可正常工作,因为

到时钟使能。在这种情况下,AMD建议将保留关系更改回

原始,位于相同的启动和捕获边缘之间。要执行此操作,您必须添加第二个

仅修改保留检查的多循环路径约束:

-end选项与set_multycle-hold命令一起使用,因为

捕获时钟必须向后移.

下图显示了应用两者后更新的设置和保持关系多循环路径约束。

为了总结此示例,以下约束对于正确定义data0_reg/C和data1_reg/D之间的二(2)的多循环路径:

对于设置乘数为四(4)的多循环,约束条件为: