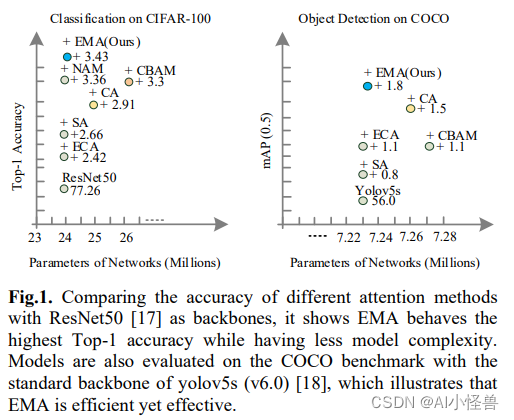

2.1建立时间和保持时间

2.1.1 D触发器的结构(两个电平触发的D触发器)

- 沿触发的触发器也叫主从触发器,内部是由两个电平触发的D触发器构成的

- 上升沿是由低电平变成高电平

- 低电平:FF1导通,数据从D到G1,建立时间

- 高电平:FF2导通,数据从G1到G2 ,保持时间

2.1.2 建立时间

- 对于任何一种触发器,在时钟触发沿前后的一个小时间窗口(建立时间)内,输入信号必须保持稳定。

- Capture触发器的时钟信号上升沿到来之前,数据需要保持稳定不变的时间。

- 输入信号应提前在时钟上升沿(假设上升沿有效)之前

T时间到达,这个T就是建立时间setup time。

2.1.3 保持时间

- 保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果hold time不够,数据同样不能被正确打入触发器

- 避免hold time violation,下一发射沿的数据在在当前setup捕获沿捕获数据之后发出

- 避免hold time violation,当前setup发射沿的数据要在上一捕获沿捕获数据之后发出

2.2 亚稳态

-

触发器无法在某个规定时间段内达到一个可确认的状态,亚稳态会带来功能的错误

-

亚稳态时

- 既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

- 触发器输出一些中间级电平,或者可能处于振荡状态。

-

亚稳态传播

-

不确定的输出电平可以沿信号通道上的各个触发器级联式传播下去

-

电路出现亚稳态其实会自动恢复,但是是恢复成稳定状态,并不一定是正确状态。这段持续的时间叫做

亚稳态的恢复时间,一般情况下这段时间不会超过一个或者两个时钟周期(取决于触发器的性能)。如果亚稳态持续时间过长(超过一个或者两个时钟周期),就有可能被下一级的触发器捕获,导致下一级触发器也处于亚稳态,这就是亚稳态的传播现象

-

2.2.1 亚稳态时

- F2的输入

A(Din)不满足F2的建立时间&保持时间,F2输出B(Dout)出现中间电压值

2.2.2 亚稳态解决办法

- 引入同步机制,防止亚稳态传播

- 降低系统时钟

- 用反应更快的Flip Flop

- 改善时钟质量,用边沿变化快速的时钟信号

多级触发器是缓解亚稳态传播的常用方法,原理也很简单,就是给亚稳态尽可能多的时间去恢复,尽量晚一点到达接收端。

触发器链只能抑制亚稳态往下传输(或者减小其往下传输的概率),并不一定能够同步正确的控制信号的值,这与亚稳态稳定后的值有关。如果稳定后错误,只能复位,但至少比亚稳态一直传播下去要好

2.2.2.1 两级触发器同步

- 使用同步器降低亚稳态发生的概率

- 亚稳态需要一段时间才能到达稳态,二级寄存器可以增加一个

clock cycle的时间使亚稳态稳定,(周期T-Tsetup为恢复时间,这段时间恢复就不会造成亚稳态传播)

- 亚稳态需要一段时间才能到达稳态,二级寄存器可以增加一个

- F2是新加的同步触发器,为了让F3采集到一个稳定的值

- 若不加F2,F3采集的就是F1的输出A,采集到的就是一个不确定的值,输出C就是不确定的值,可能会造成后级亚稳态传播

- 加F2进行两级触发器同步,F1输出A被F2采集到,此时F2输出B是一个不确定的值,但这个不确定的值只要在时钟周期减去F3的建立时间这个时间段内恢复稳定,F3采集到的就是一个稳定的值B,F3的输出C也是一个确定的值(代价就是增加了一个周期的时间)

2.2.3 MTBF

- 用二级触发器不是用来消除亚稳态,是用来降低亚稳态发生的概率的,低速场景用三级也可以,但是会增加面积