🌈个人主页:godspeed_lucip

🔥 系列专栏:计算机组成与原理基础

- 🛰️1 Cache概述

- 🛩️1.1 局部性原理

- 🛫1.1.1 空间局部性

- 🛫1.1.2 时间局部性

- 🛩️1.2 性能指标

- 🛫1.2.1 解释

- 🛫1.2.2 例题

- 🛫1.2.3 待解决的问题

- 🛩️1.3 知识总结

- 🛰️2 Cache与主存的映射

- 🪂2.1 知识总览

- 🪂2.2 全相联映射(随便放)

- 🛸2.2.1 要点

- 🛸2.2.2 CPU访问主存

- 🪂2.3 直接映射(只可以放在固定位置)

- 🛸2.3.1 要点

- 🛸2.3.2 改进

- 🛸2.3.3 缺点

- 🛸2.3.4 CPU访存

- 🪂2.4 组相联映射(可放到特定分组)

- 🛸2.4.1 要点

- 🛸2.4.2 CPU的访存

- 🪂2.5 总结

- 🛰️3 Cache替换算法

- 🚀3.1 总览

- 🚀3.2 随机算法(RAND)

- ✈️3.2.1 解释

- ✈️3.2.2 缺点

- ✈️3.2.3 优点

- ✈️3.2.4 示例

- 🚀3.3 先进先出(FIFO)

- ✈️3.3.1 解释

- ✈️3.3.2 实例

- ✈️3.3.3 优点

- ✈️3.3.4 缺点

- 🚀3.4 近期最少使用算法(LRU)

- ✈️3.4.1 解释

- ✈️3.4.2 实例

- 🚀3.5 最不经常使用算法(LFU)

- ✈️3.5.1 解释

- ✈️3.5.2 实例

- ✈️3.5.3 缺点

- 🚀3.6 总结

- 🛰️4 Cache写策略

- 🚁4.1 总览

- 🚁4.2 写命中

- 4.2.1 写回法

- 4.2.2 全写法

- 🚁4.3 写不命中

- 🚟4.3.1 解释

- 🚟4.3.2 写分配法

- 🚟4.3.3 非写分配法

- 🚁4.4 多级Cache

- 🚟4.4.1 解释

- 🚟4.4.2 注意

- 🚁4.5 总结

- 🛰️5 总结

🛰️1 Cache概述

🛩️1.1 局部性原理

🛫1.1.1 空间局部性

(1)解释

(2)说明

比如说一个数组,当我们访问a[0][0]时,其接下来的a[0][1]、a[0][2]也很有可能被接着访问,这就是局部性原理

而对于指令也是一样,一个程序中的指令通常是被顺序存放的,CPU访问了一条指令后,对于其周围的指令是很有可能接着去访问的

🛫1.1.2 时间局部性

(1)解释

(2)说明

对于一条循环指令来说(for(int i=1,i<10,i++)),i=1的加法,在未来的i=2的时候也要用到。这就是时间局部性

3. 基于局部性原理,可以将CPU目前访问的地址“周围”的部分数据放进Cache中,这样可以大幅提升CPU的运行速度

🛩️1.2 性能指标

🛫1.2.1 解释

上述的命中率是CPU分别在Cache、主存中找数据的情况,CPU也可以同时在Cache、主存中寻找数据,此时的平均访问时间就是

🛫1.2.2 例题

🛫1.2.3 待解决的问题

Cache是取目前访问的地址的“周围”的数据,那么如何界定周围?

注意:

🛩️1.3 知识总结

🛰️2 Cache与主存的映射

🪂2.1 知识总览

解决Cache与主存的数据块的对应关系的问题

🪂2.2 全相联映射(随便放)

🛸2.2.1 要点

(1)主存块可以放在Cache的任何一块上

(2)Cache中的每块都设置了一个标记位记录该主存块的地址,对于未存放数据的Cache块标记位已全0展示

(3)但是地址位为全0的主存块实际上是有资源的,所以还需要设置一个有效位(1代表有数据,0代表无数据)

🛸2.2.2 CPU访问主存

(1)前提:主存地址空间为256MB,每块行长为64kb,则:

假设CPU访问地址为:1…1101 001110

🪂2.3 直接映射(只可以放在固定位置)

🛸2.3.1 要点

(1)使主存地址对Cache内存块个数取余,得到的数字就是该主存块应该存放的Cache块编号

(2)设置了标记位与有效位,与全相联映射一致。

🛸2.3.2 改进

考虑到该方法需要将主存地址对Cache总块数取余,即地址的后三位实际上对应的是Cache块的编号,那么在Cache的标记位上,可以直接截取主存地址的前19位,因为后3位分别为000-111。

🛸2.3.3 缺点

对于一个特定的主存块来说,假如其对应的Cache内存块没有空间,那么即使其他Cache块有空间,该主存块也不可以放到有空间的Cache块中去。

🛸2.3.4 CPU访存

🪂2.4 组相联映射(可放到特定分组)

🛸2.4.1 要点

(1)将Cache块分组,主存块需要对组数进行取余,根据结果决定改主存块要放在那个Cache块组中。

(2)设定标记位与有效位

(3)标记位的改进方法与直接映射类似,对于一个块数为8的Cache,对地址位为22位的主存地址只需要保存前20位就可以了。(222/22)

🛸2.4.2 CPU的访存

🪂2.5 总结

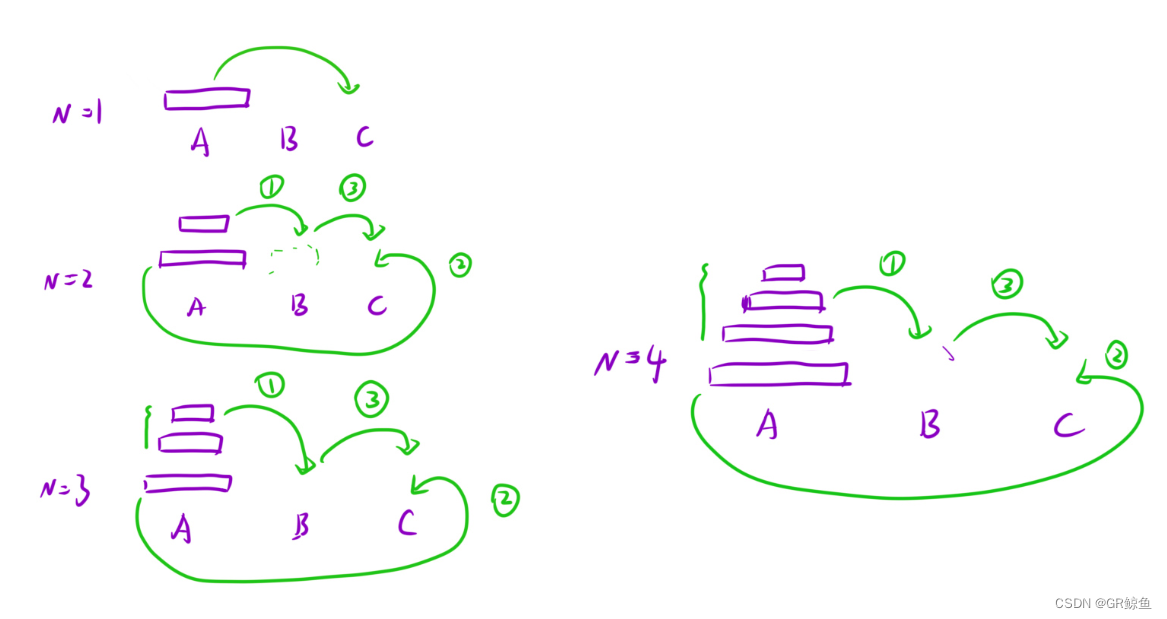

🛰️3 Cache替换算法

🚀3.1 总览

🚀3.2 随机算法(RAND)

✈️3.2.1 解释

✈️3.2.2 缺点

✈️3.2.3 优点

实现简单,原理简单

✈️3.2.4 示例

注意:当CPU在Cache中未访问到目标数据而去主存寻找时,找到的数据要立即放入Cache中去

🚀3.3 先进先出(FIFO)

✈️3.3.1 解释

✈️3.3.2 实例

✈️3.3.3 优点

✈️3.3.4 缺点

且容易出现抖动现象

🚀3.4 近期最少使用算法(LRU)

✈️3.4.1 解释

对于第一条,我们当然也可以使其加1,但是不加1其实也可以达到效果。

✈️3.4.2 实例

🚀3.5 最不经常使用算法(LFU)

✈️3.5.1 解释

✈️3.5.2 实例

✈️3.5.3 缺点

🚀3.6 总结

LRU的Cache的命中率最大,效果最好

🛰️4 Cache写策略

🚁4.1 总览

🚁4.2 写命中

解释

CPU要对一个地址进行写操作,而且这个地址已经被调入了Cache,发生了命中的情况

4.2.1 写回法

- 解释

这样做避免了每次写都将数据写回主存,节省了一些写的时间

- 注意

为了让CPU知道Cache是否发生了写操作,还需要对每个Cache块增加一个“脏位”,该位数值为1代表已经修改,为0代表没有修改

- 示意图

缺点

存在数据不一致的隐患

4.2.2 全写法

- 解释

- 注意

为了增加CPU将数据写入主存的速度,可以增加一个由SRAM(速度较快)实现的缓冲队列,CPU先将数据放入缓冲队列,当CPU暂时不再进行写操作时,缓冲队列在专门的控制电路下将数据写入主存

- 示意图

- 缺点

🚁4.3 写不命中

🚟4.3.1 解释

当CPU需要对一个地址进行写操作,且这个数据不在Cache中的时候,CPU回将数据调入Cache中

🚟4.3.2 写分配法

-

解释

-

示意图

🚟4.3.3 非写分配法

-

解释

-

也就是说,当不命中时,CPU对某个地址进行写操作时不讲数据调入Cache,只有在进行读操作时才将数据调入Cache。因为具备全写法中直接对主存进行修改的特性,所以通常搭配全写法使用

-

示意图

🚁4.4 多级Cache

🚟4.4.1 解释

🚟4.4.2 注意

低级Cache中保存的是主存的副本,而高级Cache保存的是低级Cache的副本,所以多级Cache中也存在数据同步的问题。一般来说:

🚁4.5 总结

🛰️5 总结

计算机组成原理如一座精密的交响乐团,微观中展现着电子的舞蹈,宏观中奏响着科技的交响曲。

它拆解复杂问题为简单指令,通过微处理器的默契协作,创造出无尽可能。

存储单元如记忆的灯塔,指引信息的航程。

总线是信息的大道,连接着各个功能模块,使计算机成为无比高效的智慧之器。

在计算机组成原理的魔法指导下,世界逐渐变得更加智能、便捷、创新。

渴望挑战计算机组成与原理的学习路径和掌握进阶技术?不妨点击下方链接,一同探讨更多CO的奇迹吧。我们推出了引领趋势的💻CO专栏:《计算机组成原理基础》 ,旨在深度探索CO的实际应用和创新。🌐🔍

![Cocos2dx-lua ScrollView[一]基础篇](https://img-blog.csdnimg.cn/direct/8d35bd370b854f478e54a7fd86f165b8.png)