这本书是图像处理方面ASIC与DSP比较,讲了为什么要用ASIC做图像处理,它的特点和适用场景。读到第一章,(计算卷积的)工作窗口位于图像边界时镜像扩展后的情况。

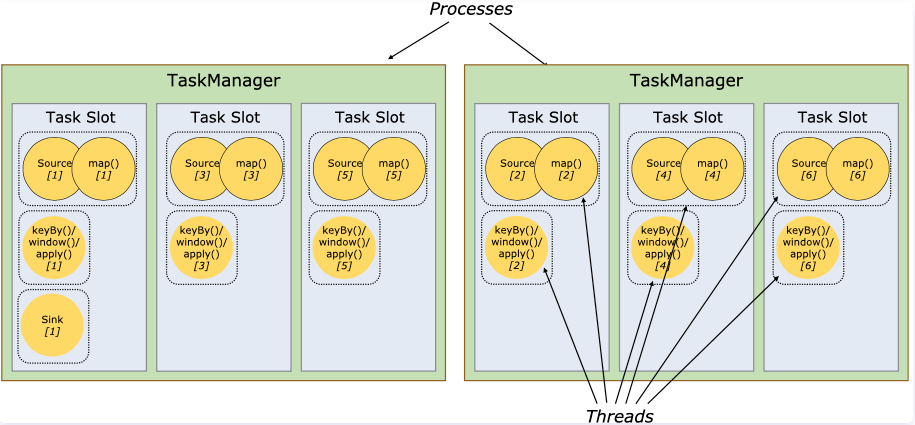

输入仍然是逐行逐列串行图像数据流,但是在工作窗口内部,根据窗口中心像素的坐标判断窗口位于图像边界的具体位置,由此决定窗口中某个寄存器的值是来自原先的移位寄存器,还是来自与之镜像行/列的寄存器。

每行有一个行缓存。许多单独的寄存器,还有多路选择器,组成了工作窗口位于图像边界时镜像扩展的电路图(schematic)。

核心思路是:多路选择器,有许多个,根据中心像素位于第几行,选择对应的选通支路。

补充网上查到的另一个角度的策略:

图像的镜像用FPGA 实现,共有四种模式:

Mode1: 原图,

Mode2:全镜像,

Mode3:水平镜像,

Mode4:垂直镜像。

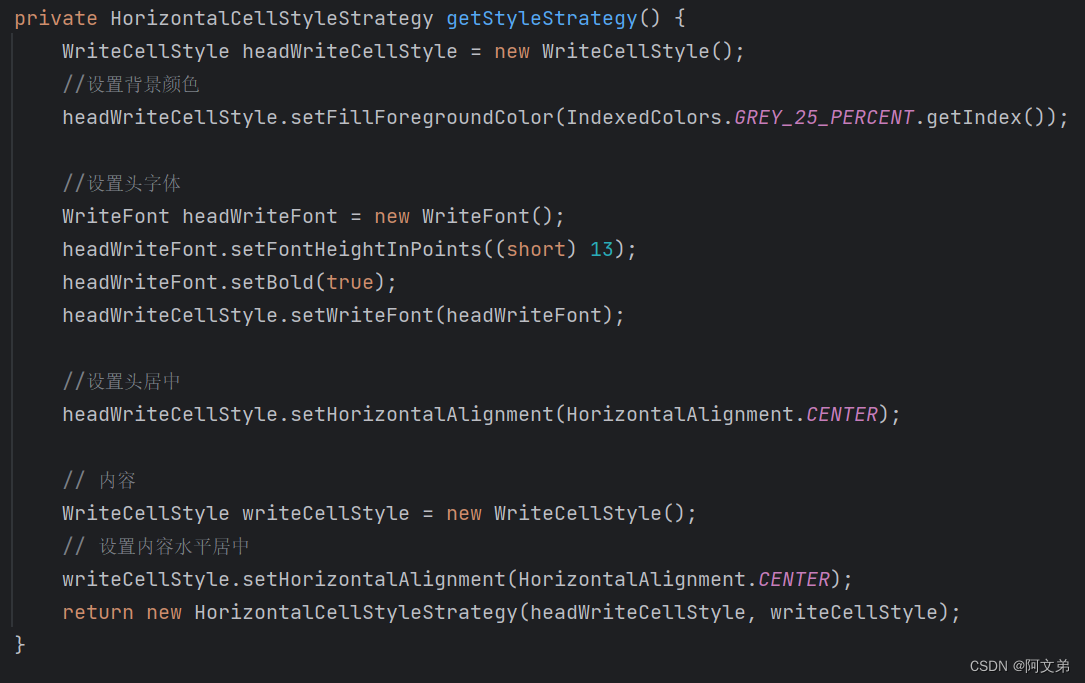

Verilog实现镜像源码:

`timescale1ns / 1ps module mirror #( parameter DW =