0. 环境

- ubuntu18

- vivado 2018.3

- mizar z7010 + ada106模块

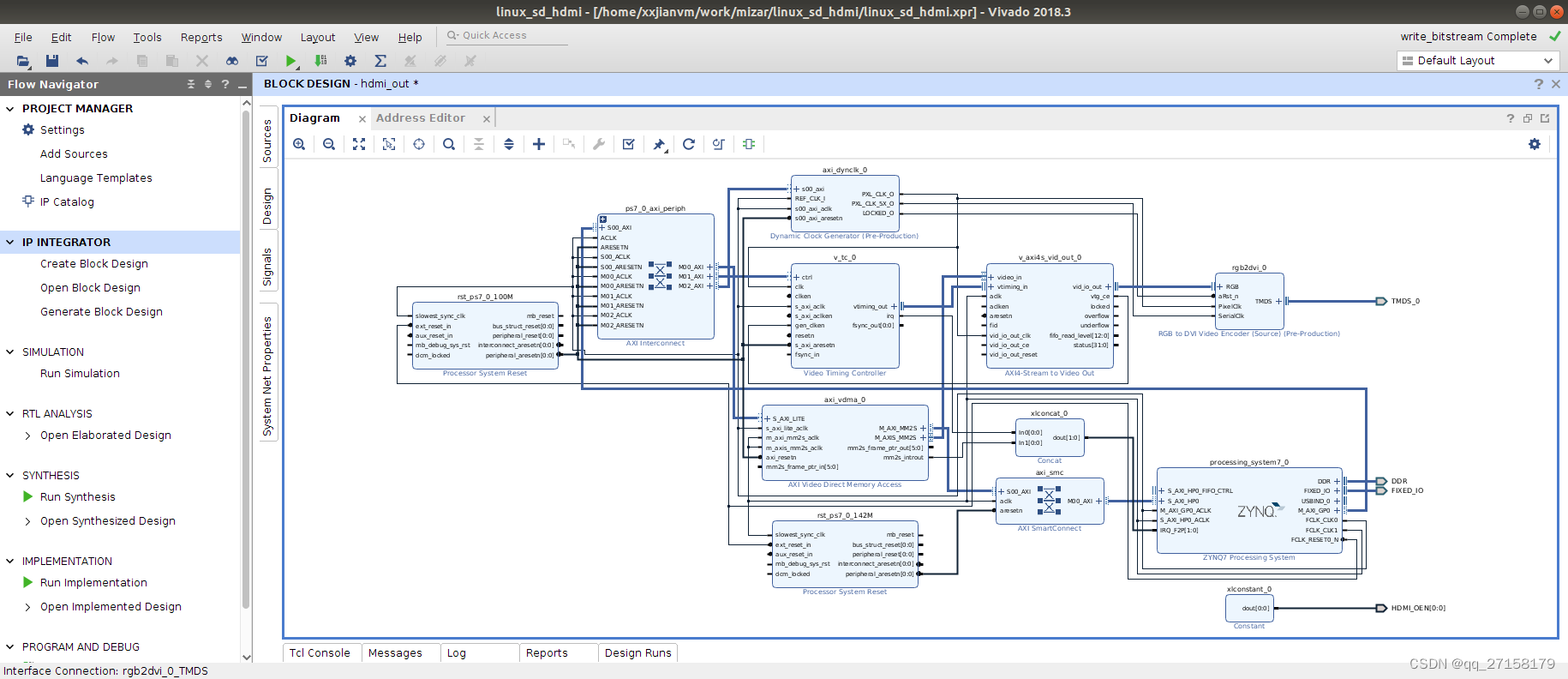

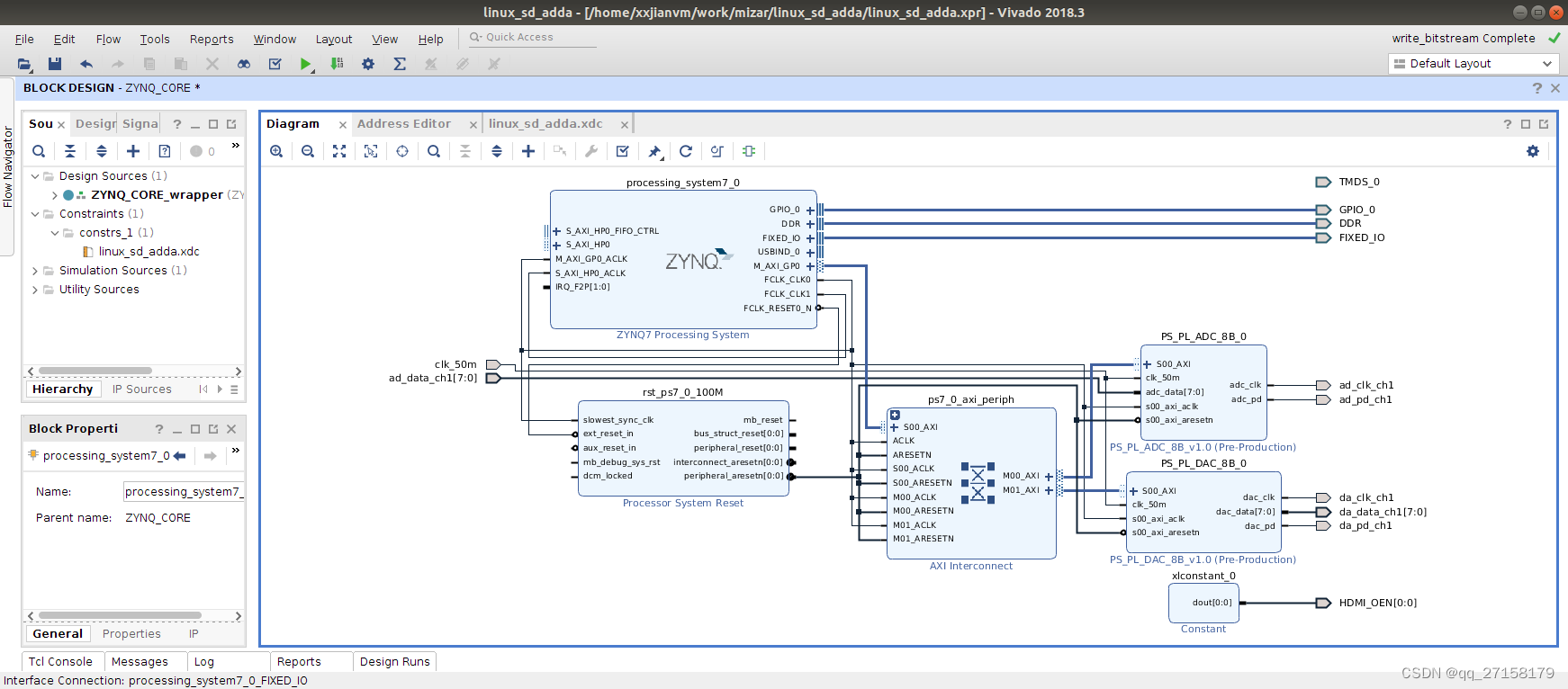

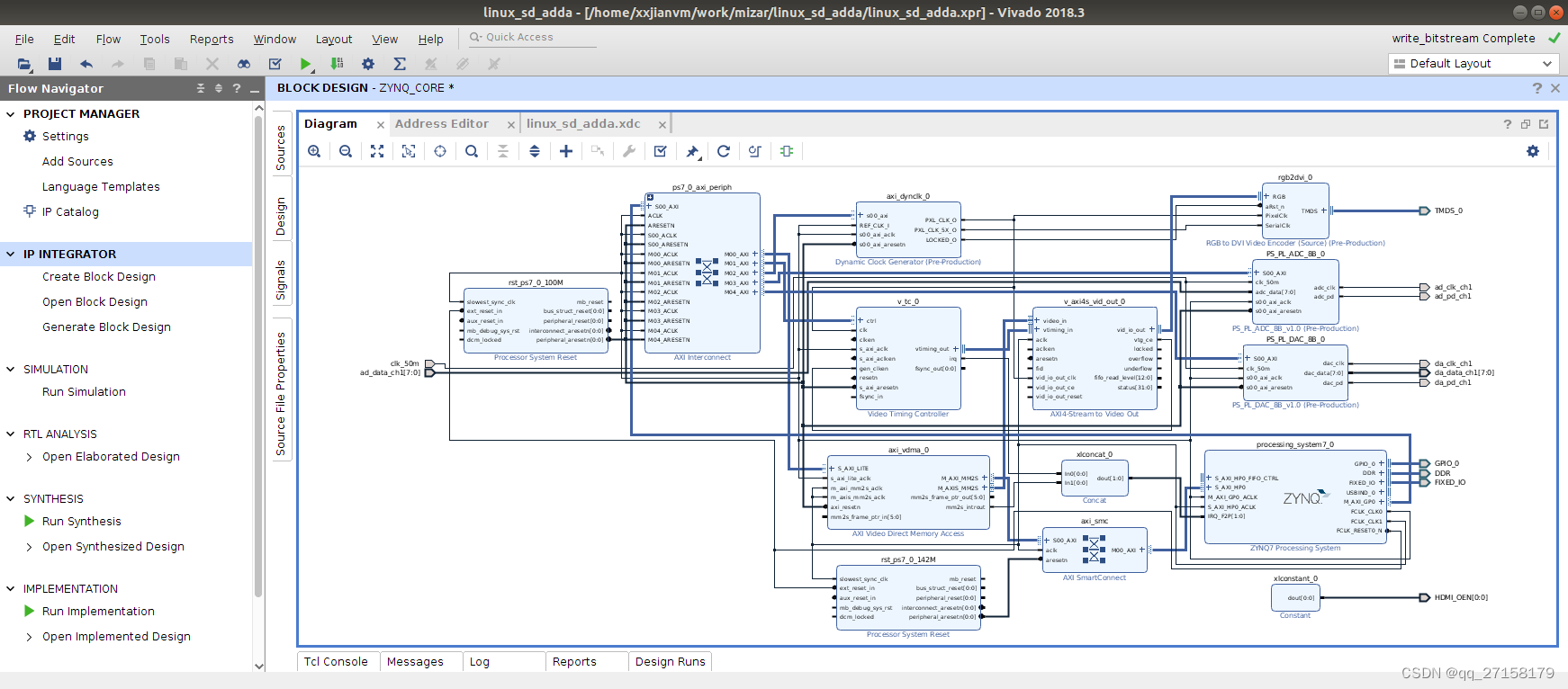

1. vivado

1.1 创建vivado工程

运行vivado

source /tools/Xilinx/Vivado/2018.3/settings64.sh

vivado&创建vivado工程

Vivado -> Create Project -> Next ->

-> Project name: linux_sd_adda

-> project location: /home/xxjianvm/work/mizar/

-> Next

-> RTL Project -> Next

-> Next

-> Next

-> Default part: xc7z010CLG400-1 -> Next

-> Finish

-> Finish

1.2 建立IP- PS_PL_DAC_8B

130个32位的寄存器定义

序号 定义

0 控制1,PS写,采样频率设置

1 控制2,PS写,高16位是DAC使能,低16位是数据长度

2 回复1,PL写,

3-129 数据,PS写

1.2.1 添加IP

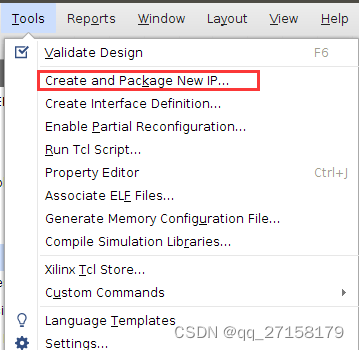

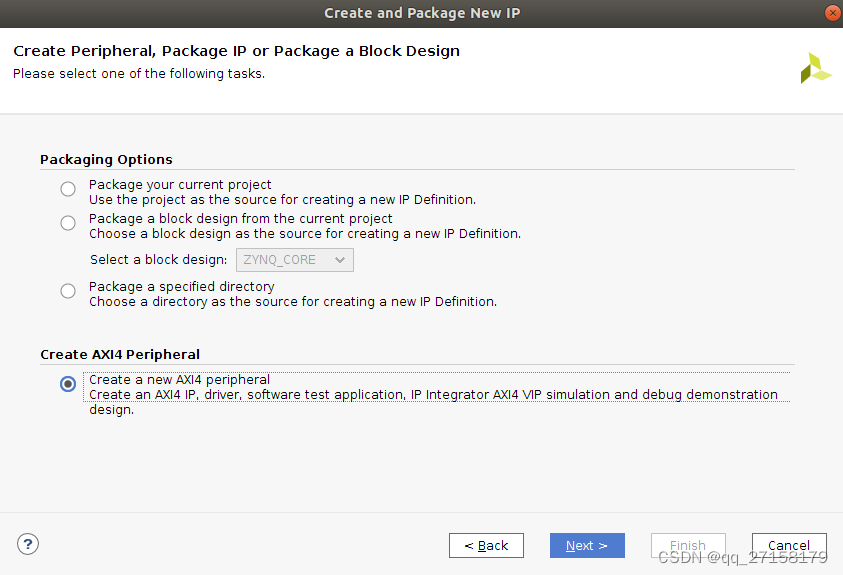

Tools -> Create and Package New IP -> Next

-> Create a new AXI4 peripheral -> Next

-> Name: PS_PL_DAC_8B

-> Description: PS_READ_WRITE_PL_REG for dac 8 bit

-> IP location: /home/xxjianvm/work/mizar/ip_repo

-> Next

-> Add Interface

-> Number of Registers: 130

-> Next

-> Create Peripheral

-> Edit IP -> Finish

1.2.2 编辑IP

1.2.2.1 基本端口定义

双击 PS_PL_DAC_8B_v1_0.v

修改第 17 行

// Users to add ports hereinput wire clk_50m,output wire dac_clk,output wire [7:0] dac_data,output wire dac_pd,// User ports ends

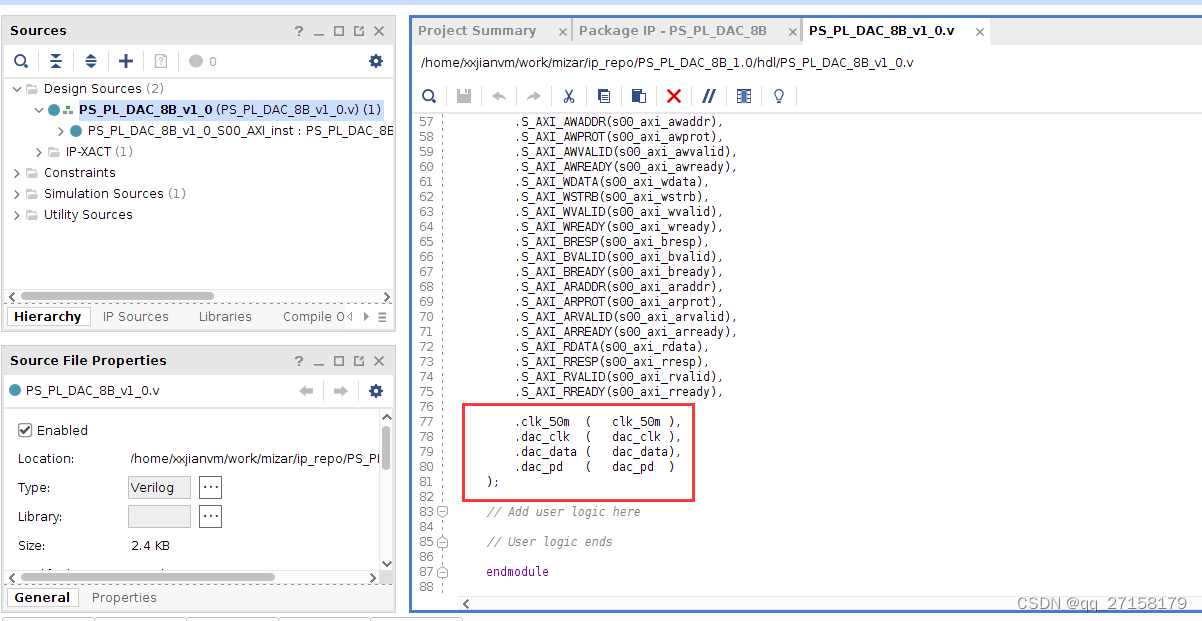

修改第 76 行:

.clk_50m ( clk_50m ),.dac_clk ( dac_clk ),.dac_data ( dac_data),.dac_pd ( dac_pd )

1.2.2.2 双击 PS_PL_DAC_8B_v1_0_S00_AXI_inst

修改端口,第17行:

// Users to add ports hereinput wire clk_50m,output wire dac_clk,output reg [7:0] dac_data,output wire dac_pd,// User ports ends

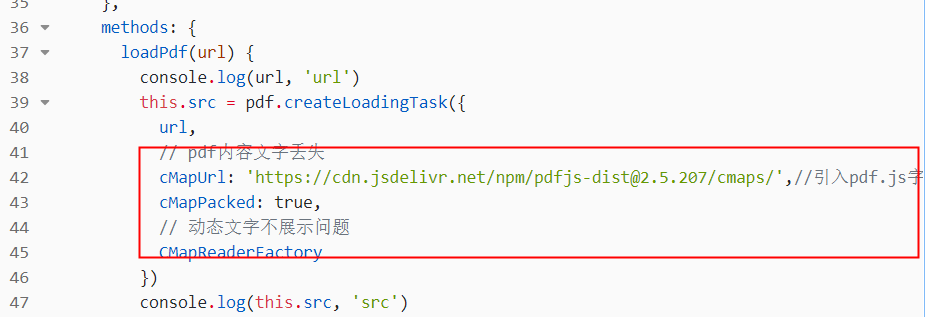

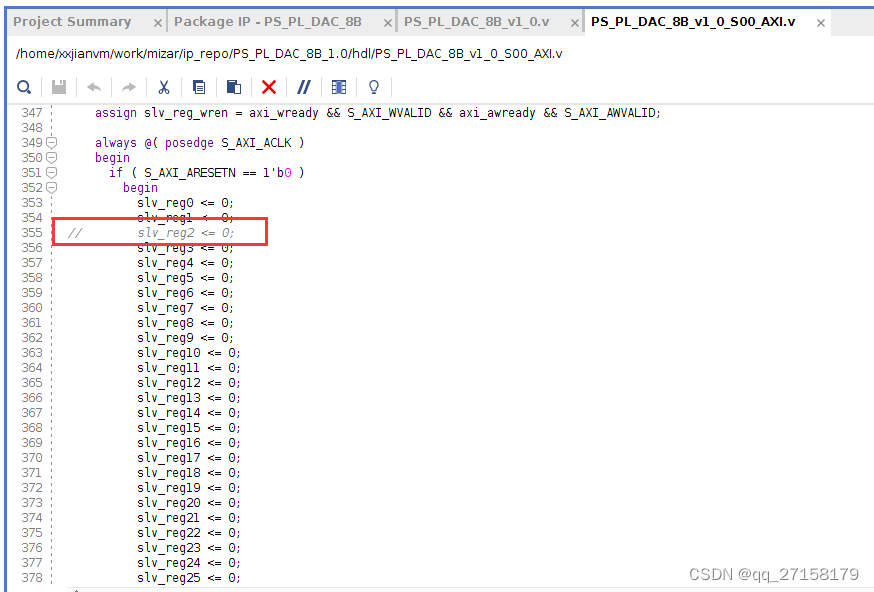

slv_reg2改为PL写。注释掉alway模块内的这几行,slv_reg2就改为PS只读不可写。

注释:

// slv_reg2 <= 0;

注释

// slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

注释

// slv_reg2 <= slv_reg2;

![]()

![]()

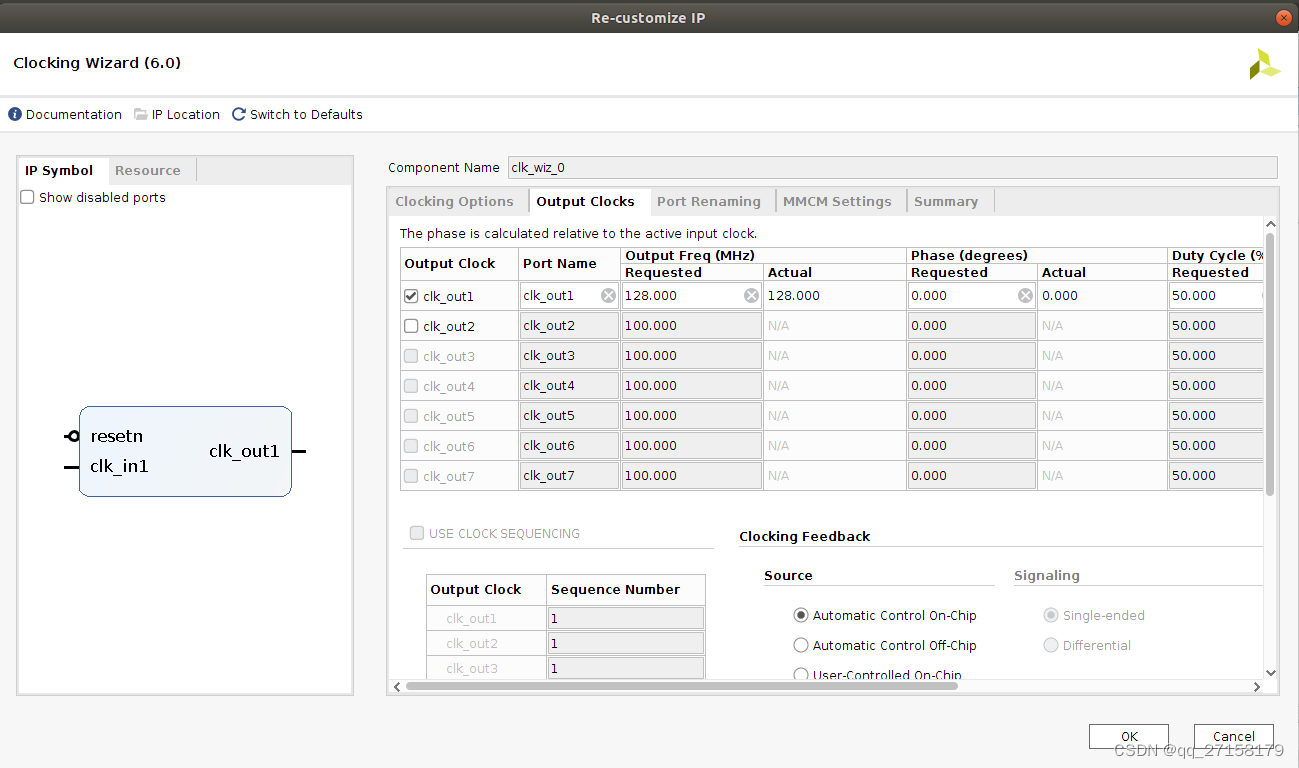

1.2.2.3 时钟信号

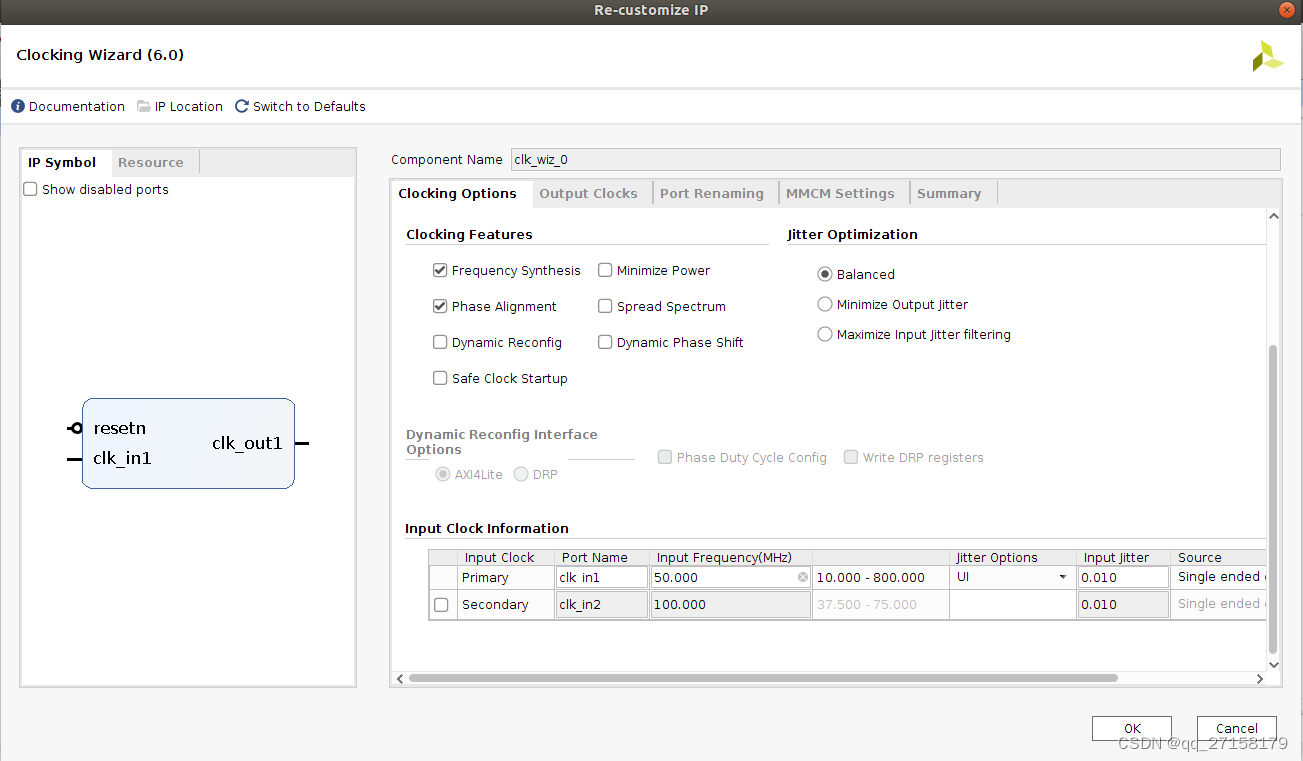

-> Project Manager -> IP Catalog -> clocking wizard ->

-> Component Name: clock

-> Clocking Options

-> Input Clock Information

-> Primary frequency: 50Mhz

-> Output Clocks

-> clk_out1: 128MHz

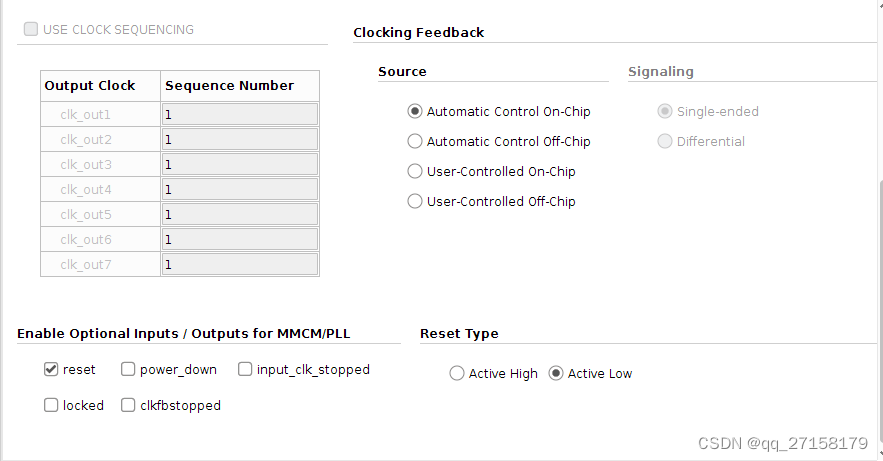

-> Enable Optional Inputs / Outputs for MMCM/PLL:

-> 取消勾选lcoked

-> Reset Type: Active Low

-> OK -> Generate

1.2.3 编写verilog文件,根据寄存器0,设置时钟

创建文件 da9708_clkswitch.v

这里寄存器0的定义是设置DAC采样频率。为了简便,这个DAC只支持几个64倍数的采样频率。

module da9708_clkswitch

(clk_128m, rst_n, slv_reg0,clk_64m, clk_25p6m,clk_12p8m,clk_6400k,clk_2560k,clk_1280k,clk_640k,clk_256k,clk_128k,clk_64k,clk_25600,clk_12800,clk_6400,clk_2560,clk_1280,clk_640,clk_256,clk_128,clk_64,clk_25p6,clk_12p8,clk_6p4,clk_dac

);input wire clk_128m;

input wire rst_n;

input wire [31:0] slv_reg0;input wire clk_64m;

input wire clk_25p6m;

input wire clk_12p8m;

input wire clk_6400k;

input wire clk_2560k;

input wire clk_1280k;

input wire clk_640k;

input wire clk_256k;

input wire clk_128k;

input wire clk_64k;

input wire clk_25600;

input wire clk_12800;

input wire clk_6400;

input wire clk_2560;

input wire clk_1280;

input wire clk_640;

input wire clk_256;

input wire clk_128;

input wire clk_64;

input wire clk_25p6; // 低速时钟用来判断按键

input wire clk_12p8;

input wire clk_6p4;output reg clk_dac; //

always @( posedge clk_128m or negedge rst_n) beginif( ~rst_n ) beginclk_dac <= 1'b0;endelse beginif ( slv_reg0 >= 32'd64_000_000 ) beginclk_dac <= clk_64m;endelse if ( slv_reg0 >= 32'd25_600_000 ) beginclk_dac <= clk_25p6m;endelse if ( slv_reg0 >= 32'd12_800_000 ) beginclk_dac <= clk_12p8m;endelse if ( slv_reg0 >= 32'd6_400_000 ) beginclk_dac <= clk_6400k;endelse if ( slv_reg0 >= 32'd2_560_000 ) beginclk_dac <= clk_2560k;endelse if ( slv_reg0 >= 32'd1_280_000 ) beginclk_dac <= clk_1280k;endelse if ( slv_reg0 >= 32'd640_000 ) beginclk_dac <= clk_640k;endelse if ( slv_reg0 >= 32'd256_000 ) beginclk_dac <= clk_256k;endelse if ( slv_reg0 >= 32'd128_000 ) beginclk_dac <= clk_128k;endelse if ( slv_reg0 >= 32'd64_000 ) beginclk_dac <= clk_64k;endelse if ( slv_reg0 >= 32'd25_600 ) beginclk_dac <= clk_25600;endelse if ( slv_reg0 >= 32'd12_800 ) beginclk_dac <= clk_12800;endelse if ( slv_reg0 >= 32'd6400 ) beginclk_dac <= clk_6400;endelse if ( slv_reg0 >= 32'd2560 ) beginclk_dac <= clk_2560;endelse if ( slv_reg0 >= 32'd1280 ) beginclk_dac <= clk_1280;endelse if ( slv_reg0 >= 32'd640 ) beginclk_dac <= clk_640;endelse if ( slv_reg0 >= 32'd256 ) beginclk_dac <= clk_256;endelse if ( slv_reg0 >= 32'd128 ) beginclk_dac <= clk_128;endelse if ( slv_reg0 >= 32'd64 ) beginclk_dac <= clk_64;endelse if ( slv_reg0 >= 32'd25 ) beginclk_dac <= clk_25p6;endelse if ( slv_reg0 >= 32'd12 ) beginclk_dac <= clk_12p8;endelse if ( slv_reg0 >= 32'd6 ) beginclk_dac <= clk_6p4;endelse beginclk_dac <= 1'b0;endend

endendmodule

1.2.4 编写verilog,对128M时钟分频

1.2.4.1 da9708_clkevery.v

module da9708_clkevery

(clk_128m, rst_n, clk_64m, clk_25p6m,clk_12p8m,clk_6400k,clk_2560k,clk_1280k,clk_640k,clk_256k,clk_128k,clk_64k,clk_25600,clk_12800,clk_6400,clk_2560,clk_1280,clk_640,clk_256,clk_128,clk_64,clk_25p6,clk_12p8,clk_6p4

);input clk_128m;

input rst_n;

output clk_64m;

output clk_25p6m;

output clk_12p8m;

output clk_6400k;

output clk_2560k;

output clk_1280k;

output clk_640k;

output clk_256k;

output clk_128k;

output clk_64k;

output clk_25600;

output clk_12800;

output clk_6400;

output clk_2560;

output clk_1280;

output clk_640;

output clk_256;

output clk_128;

output clk_64;

output clk_25p6;

output clk_12p8;

output clk_6p4;// 时钟生成模块 64m

clk_div10 clk_div10_inst_0(.clk( clk_128m ),.rstn( rst_n ) ,.clk_div2( clk_64m )

);// 时钟生成模块 25.6m, 12.8m, 6400k

clk_div2p5 clk_div2p5_inst_1(.clk( clk_64m ),.rstn( rst_n ) ,.clk_div2p5( clk_25p6m )

);

clk_div5 clk_div5_inst_1(.clk( clk_64m ),.rstn( rst_n ) ,.clk_div5( clk_12p8m )

);

clk_div10 clk_div10_inst_1(.clk( clk_64m ),.rstn( rst_n ) ,.clk_div10( clk_6400k )

);// 时钟生成模块 2560k, 1280k, 640k

clk_div2p5 clk_div2p5_inst_2(.clk( clk_6400k ),.rstn( rst_n ) ,.clk_div2p5( clk_2560k )

);

clk_div5 clk_div5_inst_2(.clk( clk_6400k ),.rstn( rst_n ) ,.clk_div5( clk_1280k )

);

clk_div10 clk_div10_inst_2(.clk( clk_6400k ),.rstn( rst_n ) ,.clk_div10( clk_640k )

);// 时钟生成模块 256k, 128k, 64k

clk_div2p5 clk_div2p5_inst_3(.clk( clk_640k ),.rstn( rst_n ) ,.clk_div2p5( clk_256k )

);

clk_div5 clk_div5_inst_3(.clk( clk_640k ),.rstn( rst_n ) ,.clk_div5( clk_128k )

);

clk_div10 clk_div10_inst_3(.clk( clk_640k ),.rstn( rst_n ) ,.clk_div10( clk_64k )

);// 时钟生成模块 25600, 12800, 6400

clk_div2p5 clk_div2p5_inst_4(.clk( clk_64k ),.rstn( rst_n ) ,.clk_div2p5( clk_25600 )

);

clk_div5 clk_div5_inst_4(.clk( clk_64k ),.rstn( rst_n ) ,.clk_div5( clk_12800 )

);

clk_div10 clk_div10_inst_4(.clk( clk_64k ),.rstn( rst_n ) ,.clk_div10( clk_6400 )

);// 时钟生成模块 2560, 1280, 640

clk_div2p5 clk_div2p5_inst_5(.clk( clk_6400 ),.rstn( rst_n ) ,.clk_div2p5( clk_2560 )

);

clk_div5 clk_div5_inst_5(.clk( clk_6400 ),.rstn( rst_n ) ,.clk_div5( clk_1280 )

);

clk_div10 clk_div10_inst_5(.clk( clk_6400 ),.rstn( rst_n ) ,.clk_div10( clk_640 )

);// 时钟生成模块 256, 128, 64

clk_div2p5 clk_div2p5_inst_6(.clk( clk_640 ),.rstn( rst_n ) ,.clk_div2p5( clk_256 )

);

clk_div5 clk_div5_inst_6(.clk( clk_640 ),.rstn( rst_n ) ,.clk_div5( clk_128 )

);

clk_div10 clk_div10_inst_6(.clk( clk_640 ),.rstn( rst_n ) ,.clk_div10( clk_64 )

);// 时钟生成模块 25.6, 12.8, 6.4

clk_div2p5 clk_div2p5_inst_7(.clk( clk_64 ),.rstn( rst_n ) ,.clk_div2p5( clk_25p6 )

);

clk_div5 clk_div5_inst_7(.clk( clk_64 ),.rstn( rst_n ) ,.clk_div5( clk_12p8 )

);

clk_div10 clk_div10_inst_7(.clk( clk_64 ),.rstn( rst_n ) ,.clk_div10( clk_6p4 )

);endmodule

1.2.4.2 clk_div10.v

网上下载的时钟10分频:

module clk_div10

# (parameter DIV_CLK = 10 )

(

input rstn ,

input clk,

output clk_div2,

output clk_div4,

output clk_div10

);//2 分频

reg clk_div2_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

clk_div2_r <= 'b0 ;

end

else begin

clk_div2_r <= ~clk_div2_r ;

end

end

assign clk_div2 = clk_div2_r ;//4 分频

reg clk_div4_r ;

always @(posedge clk_div2 or negedge rstn) begin

if (!rstn) begin

clk_div4_r <= 'b0 ;

end

else begin

clk_div4_r <= ~clk_div4_r ;

end

end

assign clk_div4 = clk_div4_r ;//N/2 计数

reg [3:0] cnt ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 'b0 ;

end

else if (cnt == (DIV_CLK/2)-1) begin

cnt <= 'b0 ;

end

else begin

cnt <= cnt + 1'b1 ;

end

end//输出时钟

reg clk_div10_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

clk_div10_r <= 1'b0 ;

end

else if (cnt == (DIV_CLK/2)-1 ) begin

clk_div10_r <= ~clk_div10_r ;

end

end

assign clk_div10 = clk_div10_r ;

endmodule1.2.4.3 clk_div5.v

时钟5分频是网上下载的。

module clk_div5#(parameter DIV_CLK = 5)(input rstn ,input clk,output clk_div5);//计数器reg [3:0] cnt ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt <= 'b0 ;endelse if (cnt == DIV_CLK-1) begincnt <= 'b0 ;endelse begincnt <= cnt + 1'b1 ;endend//在上升沿产生5分频reg clkp_div5_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginclkp_div5_r <= 1'b0 ;endelse if (cnt == (DIV_CLK>>1)-1 ) begin //计数4-8位低电平clkp_div5_r <= 0 ;endelse if (cnt == DIV_CLK-1) begin //计数 0-3 为高电平clkp_div5_r <= 1 ;endend//在下降沿产生5分频reg clkn_div5_r ;always @(negedge clk or negedge rstn) beginif (!rstn) beginclkn_div5_r <= 1'b0 ;endelse if (cnt == (DIV_CLK>>1)-1 ) begin clkn_div5_r <= 0 ;endelse if (cnt == DIV_CLK-1) begin clkn_div5_r <= 1 ;endend//或操作,往往使用基本逻辑单元库// or (clk_div5, clkp_div5_r, clkn_div5_r) ;assign clk_div5 = clkp_div5_r | clkn_div5_r ;endmodule1.2.4.4 clk_div2p5.v

时钟 2.5分频

module clk_div2p5(input clk,input rstn ,output clk_div2p5

);//计数器

parameter MUL2_DIV_CLK = 5 ;

reg [3:0] cnt ;

always @(posedge clk or negedge rstn) beginif (!rstn) begincnt <= 'b0 ;endelse if (cnt == MUL2_DIV_CLK-1) begin //计数2倍分频比cnt <= 'b0 ;endelse begincnt <= cnt + 1'b1 ;end

endreg clk_ave_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginclk_ave_r <= 1'b0 ;end//first cycle: 4 source clk cycleelse if (cnt == 0) beginclk_ave_r <= 1 ;end//2nd cycle: 3 source clk cycleelse if (cnt == (MUL2_DIV_CLK/2)+1) beginclk_ave_r <= 1 ;endelse beginclk_ave_r <= 0 ;endend//adjustreg clk_adjust_r ;always @(negedge clk or negedge rstn) beginif (!rstn) beginclk_adjust_r <= 1'b0 ;end//本次时钟只为调整一致的占空比else if (cnt == 1) beginclk_adjust_r <= 1 ;end//本次时钟只为调整一致的精确分频比else if (cnt == (MUL2_DIV_CLK/2)+1 ) beginclk_adjust_r <= 1 ;endelse beginclk_adjust_r <= 0 ;endendassign clk_div2p5 = clk_adjust_r | clk_ave_r ;endmodule1.2.5 编写dac_clk驱动

dac_clk_sw.v

封装 da9708_clkswitch.v 和 da9708_clkevery.v, 实现根据寄存器0输出dac_clk,dac_clk_sw.v

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 02/18/2024 11:40:35 AM

// Design Name:

// Module Name: dac_clk_sw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module dac_clk_sw(clk_128m, rst_n, slv_reg0,clk_dac

);input wire clk_128m;

input wire rst_n;

input wire [31:0] slv_reg0;

output wire clk_dac; // 按键选择模块

da9708_clkswitch da9708_clkswitch_inst ( .clk_128m ( clk_128m ), .rst_n ( rst_n ), .slv_reg0 ( slv_reg0 ),.clk_64m ( clk_64m ),.clk_25p6m ( clk_25p6m ),.clk_12p8m ( clk_12p8m ),.clk_6400k ( clk_6400k ),.clk_2560k ( clk_2560k ),.clk_1280k ( clk_1280k ),.clk_640k ( clk_640k ),.clk_256k ( clk_256k ),.clk_128k ( clk_128k ),.clk_64k ( clk_64k ),.clk_25600 ( clk_25600 ),.clk_12800 ( clk_12800 ),.clk_6400 ( clk_6400 ),.clk_2560 ( clk_2560 ),.clk_1280 ( clk_1280 ),.clk_640 ( clk_640 ),.clk_256 ( clk_256 ),.clk_128 ( clk_128 ),.clk_64 ( clk_64 ),.clk_25p6 ( clk_25p6 ),.clk_12p8 ( clk_12p8 ),.clk_6p4 ( clk_6p4 ),.clk_dac ( clk_dac )

);// 时钟生成模块

da9708_clkevery da9708_clkevery_inst1(.clk_128m ( clk_128m ), .rst_n ( rst_n ), .clk_64m ( clk_64m ),.clk_25p6m ( clk_25p6m ),.clk_12p8m ( clk_12p8m ),.clk_6400k ( clk_6400k ),.clk_2560k ( clk_2560k ),.clk_1280k ( clk_1280k ),.clk_640k ( clk_640k ),.clk_256k ( clk_256k ),.clk_128k ( clk_128k ),.clk_64k ( clk_64k ),.clk_25600 ( clk_25600 ),.clk_12800 ( clk_12800 ),.clk_6400 ( clk_6400 ),.clk_2560 ( clk_2560 ),.clk_1280 ( clk_1280 ),.clk_640 ( clk_640 ),.clk_256 ( clk_256 ),.clk_128 ( clk_128 ),.clk_64 ( clk_64 ),.clk_25p6 ( clk_25p6 ),.clk_12p8 ( clk_12p8 ),.clk_6p4 ( clk_6p4 )

);endmodule

1.2.6 继续修改 PS_PL_DAC_8B_v1_0_S00_AXI_inst

// Add user logic hereclk_wiz_0 inst_clk_wiz_0(.clk_in1 (clk_50m ), // input clk_in1.resetn (S_AXI_ARESETN ), // input reset.clk_out1 (clk_128m) // output clk_out1); dac_clk_sw dac_clk_sw_inst(.clk_128m ( clk_128m ), .rst_n ( S_AXI_ARESETN ), .slv_reg0 ( slv_reg0 ),.clk_dac ( dac_clk )); reg [15:0] dac_cnt = 16'd0; always @( posedge dac_clk or negedge S_AXI_ARESETN ) beginif ( S_AXI_ARESETN == 1'b0 ) begindac_cnt <= 16'd0;endelse beginif ( dac_cnt >= slv_reg1[15:0] - 1'b1 ) begindac_cnt <= 16'd0;endelse begindac_cnt <= dac_cnt + 1'b1;endendendwire [7:0] dac_buffer [507:0];

assign dac_buffer[ 0 ] = slv_reg3 [7:0];

assign dac_buffer[ 1 ] = slv_reg3 [15:8];

assign dac_buffer[ 2 ] = slv_reg3 [23:16];

assign dac_buffer[ 3 ] = slv_reg3 [31:24];

assign dac_buffer[ 4 ] = slv_reg4 [7:0];

assign dac_buffer[ 5 ] = slv_reg4 [15:8];

assign dac_buffer[ 6 ] = slv_reg4 [23:16];

assign dac_buffer[ 7 ] = slv_reg4 [31:24];

assign dac_buffer[ 8 ] = slv_reg5 [7:0];

assign dac_buffer[ 9 ] = slv_reg5 [15:8];

assign dac_buffer[ 10 ] = slv_reg5 [23:16];

assign dac_buffer[ 11 ] = slv_reg5 [31:24];

assign dac_buffer[ 12 ] = slv_reg6 [7:0];

assign dac_buffer[ 13 ] = slv_reg6 [15:8];

assign dac_buffer[ 14 ] = slv_reg6 [23:16];

assign dac_buffer[ 15 ] = slv_reg6 [31:24];

assign dac_buffer[ 16 ] = slv_reg7 [7:0];

assign dac_buffer[ 17 ] = slv_reg7 [15:8];

assign dac_buffer[ 18 ] = slv_reg7 [23:16];

assign dac_buffer[ 19 ] = slv_reg7 [31:24];

assign dac_buffer[ 20 ] = slv_reg8 [7:0];

assign dac_buffer[ 21 ] = slv_reg8 [15:8];

assign dac_buffer[ 22 ] = slv_reg8 [23:16];

assign dac_buffer[ 23 ] = slv_reg8 [31:24];

assign dac_buffer[ 24 ] = slv_reg9 [7:0];

assign dac_buffer[ 25 ] = slv_reg9 [15:8];

assign dac_buffer[ 26 ] = slv_reg9 [23:16];

assign dac_buffer[ 27 ] = slv_reg9 [31:24];

assign dac_buffer[ 28 ] = slv_reg10 [7:0];

assign dac_buffer[ 29 ] = slv_reg10 [15:8];

assign dac_buffer[ 30 ] = slv_reg10 [23:16];

assign dac_buffer[ 31 ] = slv_reg10 [31:24];

assign dac_buffer[ 32 ] = slv_reg11 [7:0];

assign dac_buffer[ 33 ] = slv_reg11 [15:8];

assign dac_buffer[ 34 ] = slv_reg11 [23:16];

assign dac_buffer[ 35 ] = slv_reg11 [31:24];

assign dac_buffer[ 36 ] = slv_reg12 [7:0];

assign dac_buffer[ 37 ] = slv_reg12 [15:8];

assign dac_buffer[ 38 ] = slv_reg12 [23:16];

assign dac_buffer[ 39 ] = slv_reg12 [31:24];

assign dac_buffer[ 40 ] = slv_reg13 [7:0];

assign dac_buffer[ 41 ] = slv_reg13 [15:8];

assign dac_buffer[ 42 ] = slv_reg13 [23:16];

assign dac_buffer[ 43 ] = slv_reg13 [31:24];

assign dac_buffer[ 44 ] = slv_reg14 [7:0];

assign dac_buffer[ 45 ] = slv_reg14 [15:8];

assign dac_buffer[ 46 ] = slv_reg14 [23:16];

assign dac_buffer[ 47 ] = slv_reg14 [31:24];

assign dac_buffer[ 48 ] = slv_reg15 [7:0];

assign dac_buffer[ 49 ] = slv_reg15 [15:8];

assign dac_buffer[ 50 ] = slv_reg15 [23:16];

assign dac_buffer[ 51 ] = slv_reg15 [31:24];

assign dac_buffer[ 52 ] = slv_reg16 [7:0];

assign dac_buffer[ 53 ] = slv_reg16 [15:8];

assign dac_buffer[ 54 ] = slv_reg16 [23:16];

assign dac_buffer[ 55 ] = slv_reg16 [31:24];

assign dac_buffer[ 56 ] = slv_reg17 [7:0];

assign dac_buffer[ 57 ] = slv_reg17 [15:8];

assign dac_buffer[ 58 ] = slv_reg17 [23:16];

assign dac_buffer[ 59 ] = slv_reg17 [31:24];

assign dac_buffer[ 60 ] = slv_reg18 [7:0];

assign dac_buffer[ 61 ] = slv_reg18 [15:8];

assign dac_buffer[ 62 ] = slv_reg18 [23:16];

assign dac_buffer[ 63 ] = slv_reg18 [31:24];

assign dac_buffer[ 64 ] = slv_reg19 [7:0];

assign dac_buffer[ 65 ] = slv_reg19 [15:8];

assign dac_buffer[ 66 ] = slv_reg19 [23:16];

assign dac_buffer[ 67 ] = slv_reg19 [31:24];

assign dac_buffer[ 68 ] = slv_reg20 [7:0];

assign dac_buffer[ 69 ] = slv_reg20 [15:8];

assign dac_buffer[ 70 ] = slv_reg20 [23:16];

assign dac_buffer[ 71 ] = slv_reg20 [31:24];

assign dac_buffer[ 72 ] = slv_reg21 [7:0];

assign dac_buffer[ 73 ] = slv_reg21 [15:8];

assign dac_buffer[ 74 ] = slv_reg21 [23:16];

assign dac_buffer[ 75 ] = slv_reg21 [31:24];

assign dac_buffer[ 76 ] = slv_reg22 [7:0];

assign dac_buffer[ 77 ] = slv_reg22 [15:8];

assign dac_buffer[ 78 ] = slv_reg22 [23:16];

assign dac_buffer[ 79 ] = slv_reg22 [31:24];

assign dac_buffer[ 80 ] = slv_reg23 [7:0];

assign dac_buffer[ 81 ] = slv_reg23 [15:8];

assign dac_buffer[ 82 ] = slv_reg23 [23:16];

assign dac_buffer[ 83 ] = slv_reg23 [31:24];

assign dac_buffer[ 84 ] = slv_reg24 [7:0];

assign dac_buffer[ 85 ] = slv_reg24 [15:8];

assign dac_buffer[ 86 ] = slv_reg24 [23:16];

assign dac_buffer[ 87 ] = slv_reg24 [31:24];

assign dac_buffer[ 88 ] = slv_reg25 [7:0];

assign dac_buffer[ 89 ] = slv_reg25 [15:8];

assign dac_buffer[ 90 ] = slv_reg25 [23:16];

assign dac_buffer[ 91 ] = slv_reg25 [31:24];

assign dac_buffer[ 92 ] = slv_reg26 [7:0];

assign dac_buffer[ 93 ] = slv_reg26 [15:8];

assign dac_buffer[ 94 ] = slv_reg26 [23:16];

assign dac_buffer[ 95 ] = slv_reg26 [31:24];

assign dac_buffer[ 96 ] = slv_reg27 [7:0];

assign dac_buffer[ 97 ] = slv_reg27 [15:8];

assign dac_buffer[ 98 ] = slv_reg27 [23:16];

assign dac_buffer[ 99 ] = slv_reg27 [31:24];

assign dac_buffer[ 100 ] = slv_reg28 [7:0];

assign dac_buffer[ 101 ] = slv_reg28 [15:8];

assign dac_buffer[ 102 ] = slv_reg28 [23:16];

assign dac_buffer[ 103 ] = slv_reg28 [31:24];

assign dac_buffer[ 104 ] = slv_reg29 [7:0];

assign dac_buffer[ 105 ] = slv_reg29 [15:8];

assign dac_buffer[ 106 ] = slv_reg29 [23:16];

assign dac_buffer[ 107 ] = slv_reg29 [31:24];

assign dac_buffer[ 108 ] = slv_reg30 [7:0];

assign dac_buffer[ 109 ] = slv_reg30 [15:8];

assign dac_buffer[ 110 ] = slv_reg30 [23:16];

assign dac_buffer[ 111 ] = slv_reg30 [31:24];

assign dac_buffer[ 112 ] = slv_reg31 [7:0];

assign dac_buffer[ 113 ] = slv_reg31 [15:8];

assign dac_buffer[ 114 ] = slv_reg31 [23:16];

assign dac_buffer[ 115 ] = slv_reg31 [31:24];

assign dac_buffer[ 116 ] = slv_reg32 [7:0];

assign dac_buffer[ 117 ] = slv_reg32 [15:8];

assign dac_buffer[ 118 ] = slv_reg32 [23:16];

assign dac_buffer[ 119 ] = slv_reg32 [31:24];

assign dac_buffer[ 120 ] = slv_reg33 [7:0];

assign dac_buffer[ 121 ] = slv_reg33 [15:8];

assign dac_buffer[ 122 ] = slv_reg33 [23:16];

assign dac_buffer[ 123 ] = slv_reg33 [31:24];

assign dac_buffer[ 124 ] = slv_reg34 [7:0];

assign dac_buffer[ 125 ] = slv_reg34 [15:8];

assign dac_buffer[ 126 ] = slv_reg34 [23:16];

assign dac_buffer[ 127 ] = slv_reg34 [31:24];

assign dac_buffer[ 128 ] = slv_reg35 [7:0];

assign dac_buffer[ 129 ] = slv_reg35 [15:8];

assign dac_buffer[ 130 ] = slv_reg35 [23:16];

assign dac_buffer[ 131 ] = slv_reg35 [31:24];

assign dac_buffer[ 132 ] = slv_reg36 [7:0];

assign dac_buffer[ 133 ] = slv_reg36 [15:8];

assign dac_buffer[ 134 ] = slv_reg36 [23:16];

assign dac_buffer[ 135 ] = slv_reg36 [31:24];

assign dac_buffer[ 136 ] = slv_reg37 [7:0];

assign dac_buffer[ 137 ] = slv_reg37 [15:8];

assign dac_buffer[ 138 ] = slv_reg37 [23:16];

assign dac_buffer[ 139 ] = slv_reg37 [31:24];

assign dac_buffer[ 140 ] = slv_reg38 [7:0];

assign dac_buffer[ 141 ] = slv_reg38 [15:8];

assign dac_buffer[ 142 ] = slv_reg38 [23:16];

assign dac_buffer[ 143 ] = slv_reg38 [31:24];

assign dac_buffer[ 144 ] = slv_reg39 [7:0];

assign dac_buffer[ 145 ] = slv_reg39 [15:8];

assign dac_buffer[ 146 ] = slv_reg39 [23:16];

assign dac_buffer[ 147 ] = slv_reg39 [31:24];

assign dac_buffer[ 148 ] = slv_reg40 [7:0];

assign dac_buffer[ 149 ] = slv_reg40 [15:8];

assign dac_buffer[ 150 ] = slv_reg40 [23:16];

assign dac_buffer[ 151 ] = slv_reg40 [31:24];

assign dac_buffer[ 152 ] = slv_reg41 [7:0];

assign dac_buffer[ 153 ] = slv_reg41 [15:8];

assign dac_buffer[ 154 ] = slv_reg41 [23:16];

assign dac_buffer[ 155 ] = slv_reg41 [31:24];

assign dac_buffer[ 156 ] = slv_reg42 [7:0];

assign dac_buffer[ 157 ] = slv_reg42 [15:8];

assign dac_buffer[ 158 ] = slv_reg42 [23:16];

assign dac_buffer[ 159 ] = slv_reg42 [31:24];

assign dac_buffer[ 160 ] = slv_reg43 [7:0];

assign dac_buffer[ 161 ] = slv_reg43 [15:8];

assign dac_buffer[ 162 ] = slv_reg43 [23:16];

assign dac_buffer[ 163 ] = slv_reg43 [31:24];

assign dac_buffer[ 164 ] = slv_reg44 [7:0];

assign dac_buffer[ 165 ] = slv_reg44 [15:8];

assign dac_buffer[ 166 ] = slv_reg44 [23:16];

assign dac_buffer[ 167 ] = slv_reg44 [31:24];

assign dac_buffer[ 168 ] = slv_reg45 [7:0];

assign dac_buffer[ 169 ] = slv_reg45 [15:8];

assign dac_buffer[ 170 ] = slv_reg45 [23:16];

assign dac_buffer[ 171 ] = slv_reg45 [31:24];

assign dac_buffer[ 172 ] = slv_reg46 [7:0];

assign dac_buffer[ 173 ] = slv_reg46 [15:8];

assign dac_buffer[ 174 ] = slv_reg46 [23:16];

assign dac_buffer[ 175 ] = slv_reg46 [31:24];

assign dac_buffer[ 176 ] = slv_reg47 [7:0];

assign dac_buffer[ 177 ] = slv_reg47 [15:8];

assign dac_buffer[ 178 ] = slv_reg47 [23:16];

assign dac_buffer[ 179 ] = slv_reg47 [31:24];

assign dac_buffer[ 180 ] = slv_reg48 [7:0];

assign dac_buffer[ 181 ] = slv_reg48 [15:8];

assign dac_buffer[ 182 ] = slv_reg48 [23:16];

assign dac_buffer[ 183 ] = slv_reg48 [31:24];

assign dac_buffer[ 184 ] = slv_reg49 [7:0];

assign dac_buffer[ 185 ] = slv_reg49 [15:8];

assign dac_buffer[ 186 ] = slv_reg49 [23:16];

assign dac_buffer[ 187 ] = slv_reg49 [31:24];

assign dac_buffer[ 188 ] = slv_reg50 [7:0];

assign dac_buffer[ 189 ] = slv_reg50 [15:8];

assign dac_buffer[ 190 ] = slv_reg50 [23:16];

assign dac_buffer[ 191 ] = slv_reg50 [31:24];

assign dac_buffer[ 192 ] = slv_reg51 [7:0];

assign dac_buffer[ 193 ] = slv_reg51 [15:8];

assign dac_buffer[ 194 ] = slv_reg51 [23:16];

assign dac_buffer[ 195 ] = slv_reg51 [31:24];

assign dac_buffer[ 196 ] = slv_reg52 [7:0];

assign dac_buffer[ 197 ] = slv_reg52 [15:8];

assign dac_buffer[ 198 ] = slv_reg52 [23:16];

assign dac_buffer[ 199 ] = slv_reg52 [31:24];

assign dac_buffer[ 200 ] = slv_reg53 [7:0];

assign dac_buffer[ 201 ] = slv_reg53 [15:8];

assign dac_buffer[ 202 ] = slv_reg53 [23:16];

assign dac_buffer[ 203 ] = slv_reg53 [31:24];

assign dac_buffer[ 204 ] = slv_reg54 [7:0];

assign dac_buffer[ 205 ] = slv_reg54 [15:8];

assign dac_buffer[ 206 ] = slv_reg54 [23:16];

assign dac_buffer[ 207 ] = slv_reg54 [31:24];

assign dac_buffer[ 208 ] = slv_reg55 [7:0];

assign dac_buffer[ 209 ] = slv_reg55 [15:8];

assign dac_buffer[ 210 ] = slv_reg55 [23:16];

assign dac_buffer[ 211 ] = slv_reg55 [31:24];

assign dac_buffer[ 212 ] = slv_reg56 [7:0];

assign dac_buffer[ 213 ] = slv_reg56 [15:8];

assign dac_buffer[ 214 ] = slv_reg56 [23:16];

assign dac_buffer[ 215 ] = slv_reg56 [31:24];

assign dac_buffer[ 216 ] = slv_reg57 [7:0];

assign dac_buffer[ 217 ] = slv_reg57 [15:8];

assign dac_buffer[ 218 ] = slv_reg57 [23:16];

assign dac_buffer[ 219 ] = slv_reg57 [31:24];

assign dac_buffer[ 220 ] = slv_reg58 [7:0];

assign dac_buffer[ 221 ] = slv_reg58 [15:8];

assign dac_buffer[ 222 ] = slv_reg58 [23:16];

assign dac_buffer[ 223 ] = slv_reg58 [31:24];

assign dac_buffer[ 224 ] = slv_reg59 [7:0];

assign dac_buffer[ 225 ] = slv_reg59 [15:8];

assign dac_buffer[ 226 ] = slv_reg59 [23:16];

assign dac_buffer[ 227 ] = slv_reg59 [31:24];

assign dac_buffer[ 228 ] = slv_reg60 [7:0];

assign dac_buffer[ 229 ] = slv_reg60 [15:8];

assign dac_buffer[ 230 ] = slv_reg60 [23:16];

assign dac_buffer[ 231 ] = slv_reg60 [31:24];

assign dac_buffer[ 232 ] = slv_reg61 [7:0];

assign dac_buffer[ 233 ] = slv_reg61 [15:8];

assign dac_buffer[ 234 ] = slv_reg61 [23:16];

assign dac_buffer[ 235 ] = slv_reg61 [31:24];

assign dac_buffer[ 236 ] = slv_reg62 [7:0];

assign dac_buffer[ 237 ] = slv_reg62 [15:8];

assign dac_buffer[ 238 ] = slv_reg62 [23:16];

assign dac_buffer[ 239 ] = slv_reg62 [31:24];

assign dac_buffer[ 240 ] = slv_reg63 [7:0];

assign dac_buffer[ 241 ] = slv_reg63 [15:8];

assign dac_buffer[ 242 ] = slv_reg63 [23:16];

assign dac_buffer[ 243 ] = slv_reg63 [31:24];

assign dac_buffer[ 244 ] = slv_reg64 [7:0];

assign dac_buffer[ 245 ] = slv_reg64 [15:8];

assign dac_buffer[ 246 ] = slv_reg64 [23:16];

assign dac_buffer[ 247 ] = slv_reg64 [31:24];

assign dac_buffer[ 248 ] = slv_reg65 [7:0];

assign dac_buffer[ 249 ] = slv_reg65 [15:8];

assign dac_buffer[ 250 ] = slv_reg65 [23:16];

assign dac_buffer[ 251 ] = slv_reg65 [31:24];

assign dac_buffer[ 252 ] = slv_reg66 [7:0];

assign dac_buffer[ 253 ] = slv_reg66 [15:8];

assign dac_buffer[ 254 ] = slv_reg66 [23:16];

assign dac_buffer[ 255 ] = slv_reg66 [31:24];

assign dac_buffer[ 256 ] = slv_reg67 [7:0];

assign dac_buffer[ 257 ] = slv_reg67 [15:8];

assign dac_buffer[ 258 ] = slv_reg67 [23:16];

assign dac_buffer[ 259 ] = slv_reg67 [31:24];

assign dac_buffer[ 260 ] = slv_reg68 [7:0];

assign dac_buffer[ 261 ] = slv_reg68 [15:8];

assign dac_buffer[ 262 ] = slv_reg68 [23:16];

assign dac_buffer[ 263 ] = slv_reg68 [31:24];

assign dac_buffer[ 264 ] = slv_reg69 [7:0];

assign dac_buffer[ 265 ] = slv_reg69 [15:8];

assign dac_buffer[ 266 ] = slv_reg69 [23:16];

assign dac_buffer[ 267 ] = slv_reg69 [31:24];

assign dac_buffer[ 268 ] = slv_reg70 [7:0];

assign dac_buffer[ 269 ] = slv_reg70 [15:8];

assign dac_buffer[ 270 ] = slv_reg70 [23:16];

assign dac_buffer[ 271 ] = slv_reg70 [31:24];

assign dac_buffer[ 272 ] = slv_reg71 [7:0];

assign dac_buffer[ 273 ] = slv_reg71 [15:8];

assign dac_buffer[ 274 ] = slv_reg71 [23:16];

assign dac_buffer[ 275 ] = slv_reg71 [31:24];

assign dac_buffer[ 276 ] = slv_reg72 [7:0];

assign dac_buffer[ 277 ] = slv_reg72 [15:8];

assign dac_buffer[ 278 ] = slv_reg72 [23:16];

assign dac_buffer[ 279 ] = slv_reg72 [31:24];

assign dac_buffer[ 280 ] = slv_reg73 [7:0];

assign dac_buffer[ 281 ] = slv_reg73 [15:8];

assign dac_buffer[ 282 ] = slv_reg73 [23:16];

assign dac_buffer[ 283 ] = slv_reg73 [31:24];

assign dac_buffer[ 284 ] = slv_reg74 [7:0];

assign dac_buffer[ 285 ] = slv_reg74 [15:8];

assign dac_buffer[ 286 ] = slv_reg74 [23:16];

assign dac_buffer[ 287 ] = slv_reg74 [31:24];

assign dac_buffer[ 288 ] = slv_reg75 [7:0];

assign dac_buffer[ 289 ] = slv_reg75 [15:8];

assign dac_buffer[ 290 ] = slv_reg75 [23:16];

assign dac_buffer[ 291 ] = slv_reg75 [31:24];

assign dac_buffer[ 292 ] = slv_reg76 [7:0];

assign dac_buffer[ 293 ] = slv_reg76 [15:8];

assign dac_buffer[ 294 ] = slv_reg76 [23:16];

assign dac_buffer[ 295 ] = slv_reg76 [31:24];

assign dac_buffer[ 296 ] = slv_reg77 [7:0];

assign dac_buffer[ 297 ] = slv_reg77 [15:8];

assign dac_buffer[ 298 ] = slv_reg77 [23:16];

assign dac_buffer[ 299 ] = slv_reg77 [31:24];

assign dac_buffer[ 300 ] = slv_reg78 [7:0];

assign dac_buffer[ 301 ] = slv_reg78 [15:8];

assign dac_buffer[ 302 ] = slv_reg78 [23:16];

assign dac_buffer[ 303 ] = slv_reg78 [31:24];

assign dac_buffer[ 304 ] = slv_reg79 [7:0];

assign dac_buffer[ 305 ] = slv_reg79 [15:8];

assign dac_buffer[ 306 ] = slv_reg79 [23:16];

assign dac_buffer[ 307 ] = slv_reg79 [31:24];

assign dac_buffer[ 308 ] = slv_reg80 [7:0];

assign dac_buffer[ 309 ] = slv_reg80 [15:8];

assign dac_buffer[ 310 ] = slv_reg80 [23:16];

assign dac_buffer[ 311 ] = slv_reg80 [31:24];

assign dac_buffer[ 312 ] = slv_reg81 [7:0];

assign dac_buffer[ 313 ] = slv_reg81 [15:8];

assign dac_buffer[ 314 ] = slv_reg81 [23:16];

assign dac_buffer[ 315 ] = slv_reg81 [31:24];

assign dac_buffer[ 316 ] = slv_reg82 [7:0];

assign dac_buffer[ 317 ] = slv_reg82 [15:8];

assign dac_buffer[ 318 ] = slv_reg82 [23:16];

assign dac_buffer[ 319 ] = slv_reg82 [31:24];

assign dac_buffer[ 320 ] = slv_reg83 [7:0];

assign dac_buffer[ 321 ] = slv_reg83 [15:8];

assign dac_buffer[ 322 ] = slv_reg83 [23:16];

assign dac_buffer[ 323 ] = slv_reg83 [31:24];

assign dac_buffer[ 324 ] = slv_reg84 [7:0];

assign dac_buffer[ 325 ] = slv_reg84 [15:8];

assign dac_buffer[ 326 ] = slv_reg84 [23:16];

assign dac_buffer[ 327 ] = slv_reg84 [31:24];

assign dac_buffer[ 328 ] = slv_reg85 [7:0];

assign dac_buffer[ 329 ] = slv_reg85 [15:8];

assign dac_buffer[ 330 ] = slv_reg85 [23:16];

assign dac_buffer[ 331 ] = slv_reg85 [31:24];

assign dac_buffer[ 332 ] = slv_reg86 [7:0];

assign dac_buffer[ 333 ] = slv_reg86 [15:8];

assign dac_buffer[ 334 ] = slv_reg86 [23:16];

assign dac_buffer[ 335 ] = slv_reg86 [31:24];

assign dac_buffer[ 336 ] = slv_reg87 [7:0];

assign dac_buffer[ 337 ] = slv_reg87 [15:8];

assign dac_buffer[ 338 ] = slv_reg87 [23:16];

assign dac_buffer[ 339 ] = slv_reg87 [31:24];

assign dac_buffer[ 340 ] = slv_reg88 [7:0];

assign dac_buffer[ 341 ] = slv_reg88 [15:8];

assign dac_buffer[ 342 ] = slv_reg88 [23:16];

assign dac_buffer[ 343 ] = slv_reg88 [31:24];

assign dac_buffer[ 344 ] = slv_reg89 [7:0];

assign dac_buffer[ 345 ] = slv_reg89 [15:8];

assign dac_buffer[ 346 ] = slv_reg89 [23:16];

assign dac_buffer[ 347 ] = slv_reg89 [31:24];

assign dac_buffer[ 348 ] = slv_reg90 [7:0];

assign dac_buffer[ 349 ] = slv_reg90 [15:8];

assign dac_buffer[ 350 ] = slv_reg90 [23:16];

assign dac_buffer[ 351 ] = slv_reg90 [31:24];

assign dac_buffer[ 352 ] = slv_reg91 [7:0];

assign dac_buffer[ 353 ] = slv_reg91 [15:8];

assign dac_buffer[ 354 ] = slv_reg91 [23:16];

assign dac_buffer[ 355 ] = slv_reg91 [31:24];

assign dac_buffer[ 356 ] = slv_reg92 [7:0];

assign dac_buffer[ 357 ] = slv_reg92 [15:8];

assign dac_buffer[ 358 ] = slv_reg92 [23:16];

assign dac_buffer[ 359 ] = slv_reg92 [31:24];

assign dac_buffer[ 360 ] = slv_reg93 [7:0];

assign dac_buffer[ 361 ] = slv_reg93 [15:8];

assign dac_buffer[ 362 ] = slv_reg93 [23:16];

assign dac_buffer[ 363 ] = slv_reg93 [31:24];

assign dac_buffer[ 364 ] = slv_reg94 [7:0];

assign dac_buffer[ 365 ] = slv_reg94 [15:8];

assign dac_buffer[ 366 ] = slv_reg94 [23:16];

assign dac_buffer[ 367 ] = slv_reg94 [31:24];

assign dac_buffer[ 368 ] = slv_reg95 [7:0];

assign dac_buffer[ 369 ] = slv_reg95 [15:8];

assign dac_buffer[ 370 ] = slv_reg95 [23:16];

assign dac_buffer[ 371 ] = slv_reg95 [31:24];

assign dac_buffer[ 372 ] = slv_reg96 [7:0];

assign dac_buffer[ 373 ] = slv_reg96 [15:8];

assign dac_buffer[ 374 ] = slv_reg96 [23:16];

assign dac_buffer[ 375 ] = slv_reg96 [31:24];

assign dac_buffer[ 376 ] = slv_reg97 [7:0];

assign dac_buffer[ 377 ] = slv_reg97 [15:8];

assign dac_buffer[ 378 ] = slv_reg97 [23:16];

assign dac_buffer[ 379 ] = slv_reg97 [31:24];

assign dac_buffer[ 380 ] = slv_reg98 [7:0];

assign dac_buffer[ 381 ] = slv_reg98 [15:8];

assign dac_buffer[ 382 ] = slv_reg98 [23:16];

assign dac_buffer[ 383 ] = slv_reg98 [31:24];

assign dac_buffer[ 384 ] = slv_reg99 [7:0];

assign dac_buffer[ 385 ] = slv_reg99 [15:8];

assign dac_buffer[ 386 ] = slv_reg99 [23:16];

assign dac_buffer[ 387 ] = slv_reg99 [31:24];

assign dac_buffer[ 388 ] = slv_reg100 [7:0];

assign dac_buffer[ 389 ] = slv_reg100 [15:8];

assign dac_buffer[ 390 ] = slv_reg100 [23:16];

assign dac_buffer[ 391 ] = slv_reg100 [31:24];

assign dac_buffer[ 392 ] = slv_reg101 [7:0];

assign dac_buffer[ 393 ] = slv_reg101 [15:8];

assign dac_buffer[ 394 ] = slv_reg101 [23:16];

assign dac_buffer[ 395 ] = slv_reg101 [31:24];

assign dac_buffer[ 396 ] = slv_reg102 [7:0];

assign dac_buffer[ 397 ] = slv_reg102 [15:8];

assign dac_buffer[ 398 ] = slv_reg102 [23:16];

assign dac_buffer[ 399 ] = slv_reg102 [31:24];

assign dac_buffer[ 400 ] = slv_reg103 [7:0];

assign dac_buffer[ 401 ] = slv_reg103 [15:8];

assign dac_buffer[ 402 ] = slv_reg103 [23:16];

assign dac_buffer[ 403 ] = slv_reg103 [31:24];

assign dac_buffer[ 404 ] = slv_reg104 [7:0];

assign dac_buffer[ 405 ] = slv_reg104 [15:8];

assign dac_buffer[ 406 ] = slv_reg104 [23:16];

assign dac_buffer[ 407 ] = slv_reg104 [31:24];

assign dac_buffer[ 408 ] = slv_reg105 [7:0];

assign dac_buffer[ 409 ] = slv_reg105 [15:8];

assign dac_buffer[ 410 ] = slv_reg105 [23:16];

assign dac_buffer[ 411 ] = slv_reg105 [31:24];

assign dac_buffer[ 412 ] = slv_reg106 [7:0];

assign dac_buffer[ 413 ] = slv_reg106 [15:8];

assign dac_buffer[ 414 ] = slv_reg106 [23:16];

assign dac_buffer[ 415 ] = slv_reg106 [31:24];

assign dac_buffer[ 416 ] = slv_reg107 [7:0];

assign dac_buffer[ 417 ] = slv_reg107 [15:8];

assign dac_buffer[ 418 ] = slv_reg107 [23:16];

assign dac_buffer[ 419 ] = slv_reg107 [31:24];

assign dac_buffer[ 420 ] = slv_reg108 [7:0];

assign dac_buffer[ 421 ] = slv_reg108 [15:8];

assign dac_buffer[ 422 ] = slv_reg108 [23:16];

assign dac_buffer[ 423 ] = slv_reg108 [31:24];

assign dac_buffer[ 424 ] = slv_reg109 [7:0];

assign dac_buffer[ 425 ] = slv_reg109 [15:8];

assign dac_buffer[ 426 ] = slv_reg109 [23:16];

assign dac_buffer[ 427 ] = slv_reg109 [31:24];

assign dac_buffer[ 428 ] = slv_reg110 [7:0];

assign dac_buffer[ 429 ] = slv_reg110 [15:8];

assign dac_buffer[ 430 ] = slv_reg110 [23:16];

assign dac_buffer[ 431 ] = slv_reg110 [31:24];

assign dac_buffer[ 432 ] = slv_reg111 [7:0];

assign dac_buffer[ 433 ] = slv_reg111 [15:8];

assign dac_buffer[ 434 ] = slv_reg111 [23:16];

assign dac_buffer[ 435 ] = slv_reg111 [31:24];

assign dac_buffer[ 436 ] = slv_reg112 [7:0];

assign dac_buffer[ 437 ] = slv_reg112 [15:8];

assign dac_buffer[ 438 ] = slv_reg112 [23:16];

assign dac_buffer[ 439 ] = slv_reg112 [31:24];

assign dac_buffer[ 440 ] = slv_reg113 [7:0];

assign dac_buffer[ 441 ] = slv_reg113 [15:8];

assign dac_buffer[ 442 ] = slv_reg113 [23:16];

assign dac_buffer[ 443 ] = slv_reg113 [31:24];

assign dac_buffer[ 444 ] = slv_reg114 [7:0];

assign dac_buffer[ 445 ] = slv_reg114 [15:8];

assign dac_buffer[ 446 ] = slv_reg114 [23:16];

assign dac_buffer[ 447 ] = slv_reg114 [31:24];

assign dac_buffer[ 448 ] = slv_reg115 [7:0];

assign dac_buffer[ 449 ] = slv_reg115 [15:8];

assign dac_buffer[ 450 ] = slv_reg115 [23:16];

assign dac_buffer[ 451 ] = slv_reg115 [31:24];

assign dac_buffer[ 452 ] = slv_reg116 [7:0];

assign dac_buffer[ 453 ] = slv_reg116 [15:8];

assign dac_buffer[ 454 ] = slv_reg116 [23:16];

assign dac_buffer[ 455 ] = slv_reg116 [31:24];

assign dac_buffer[ 456 ] = slv_reg117 [7:0];

assign dac_buffer[ 457 ] = slv_reg117 [15:8];

assign dac_buffer[ 458 ] = slv_reg117 [23:16];

assign dac_buffer[ 459 ] = slv_reg117 [31:24];

assign dac_buffer[ 460 ] = slv_reg118 [7:0];

assign dac_buffer[ 461 ] = slv_reg118 [15:8];

assign dac_buffer[ 462 ] = slv_reg118 [23:16];

assign dac_buffer[ 463 ] = slv_reg118 [31:24];

assign dac_buffer[ 464 ] = slv_reg119 [7:0];

assign dac_buffer[ 465 ] = slv_reg119 [15:8];

assign dac_buffer[ 466 ] = slv_reg119 [23:16];

assign dac_buffer[ 467 ] = slv_reg119 [31:24];

assign dac_buffer[ 468 ] = slv_reg120 [7:0];

assign dac_buffer[ 469 ] = slv_reg120 [15:8];

assign dac_buffer[ 470 ] = slv_reg120 [23:16];

assign dac_buffer[ 471 ] = slv_reg120 [31:24];

assign dac_buffer[ 472 ] = slv_reg121 [7:0];

assign dac_buffer[ 473 ] = slv_reg121 [15:8];

assign dac_buffer[ 474 ] = slv_reg121 [23:16];

assign dac_buffer[ 475 ] = slv_reg121 [31:24];

assign dac_buffer[ 476 ] = slv_reg122 [7:0];

assign dac_buffer[ 477 ] = slv_reg122 [15:8];

assign dac_buffer[ 478 ] = slv_reg122 [23:16];

assign dac_buffer[ 479 ] = slv_reg122 [31:24];

assign dac_buffer[ 480 ] = slv_reg123 [7:0];

assign dac_buffer[ 481 ] = slv_reg123 [15:8];

assign dac_buffer[ 482 ] = slv_reg123 [23:16];

assign dac_buffer[ 483 ] = slv_reg123 [31:24];

assign dac_buffer[ 484 ] = slv_reg124 [7:0];

assign dac_buffer[ 485 ] = slv_reg124 [15:8];

assign dac_buffer[ 486 ] = slv_reg124 [23:16];

assign dac_buffer[ 487 ] = slv_reg124 [31:24];

assign dac_buffer[ 488 ] = slv_reg125 [7:0];

assign dac_buffer[ 489 ] = slv_reg125 [15:8];

assign dac_buffer[ 490 ] = slv_reg125 [23:16];

assign dac_buffer[ 491 ] = slv_reg125 [31:24];

assign dac_buffer[ 492 ] = slv_reg126 [7:0];

assign dac_buffer[ 493 ] = slv_reg126 [15:8];

assign dac_buffer[ 494 ] = slv_reg126 [23:16];

assign dac_buffer[ 495 ] = slv_reg126 [31:24];

assign dac_buffer[ 496 ] = slv_reg127 [7:0];

assign dac_buffer[ 497 ] = slv_reg127 [15:8];

assign dac_buffer[ 498 ] = slv_reg127 [23:16];

assign dac_buffer[ 499 ] = slv_reg127 [31:24];

assign dac_buffer[ 500 ] = slv_reg128 [7:0];

assign dac_buffer[ 501 ] = slv_reg128 [15:8];

assign dac_buffer[ 502 ] = slv_reg128 [23:16];

assign dac_buffer[ 503 ] = slv_reg128 [31:24];

assign dac_buffer[ 504 ] = slv_reg129 [7:0];

assign dac_buffer[ 505 ] = slv_reg129 [15:8];

assign dac_buffer[ 506 ] = slv_reg129 [23:16];

assign dac_buffer[ 507 ] = slv_reg129 [31:24];always @( posedge dac_clk ) beginif ( slv_reg1[16] == 1'b0 ) begindac_data <= 8'd0;endelse begindac_data <= dac_buffer[dac_cnt];endendassign dac_pd = ~slv_reg1[16];// User logic ends

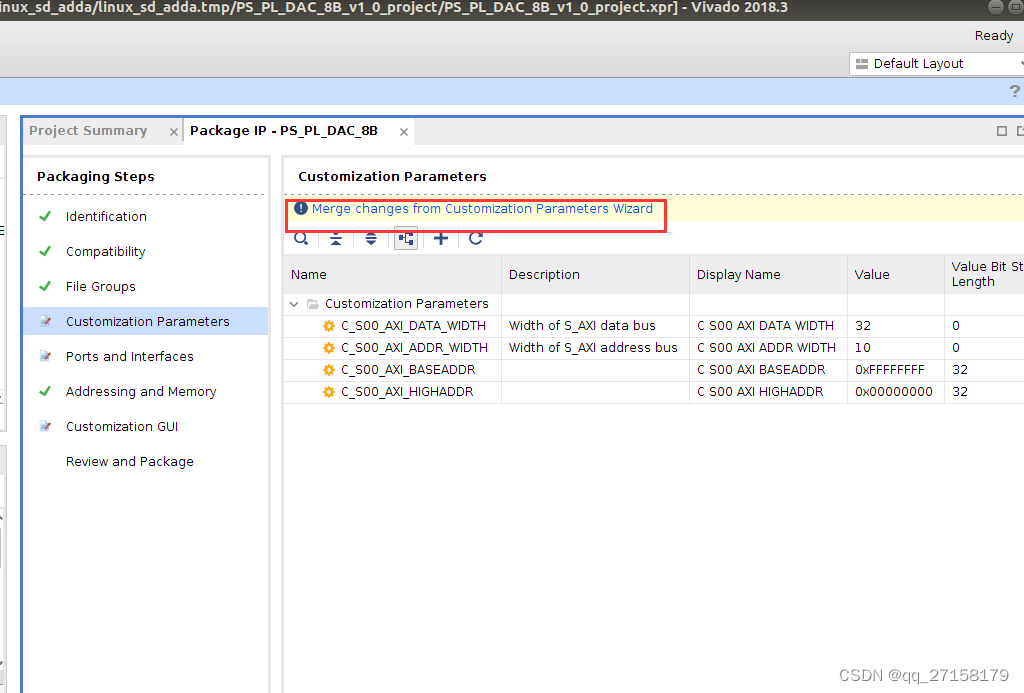

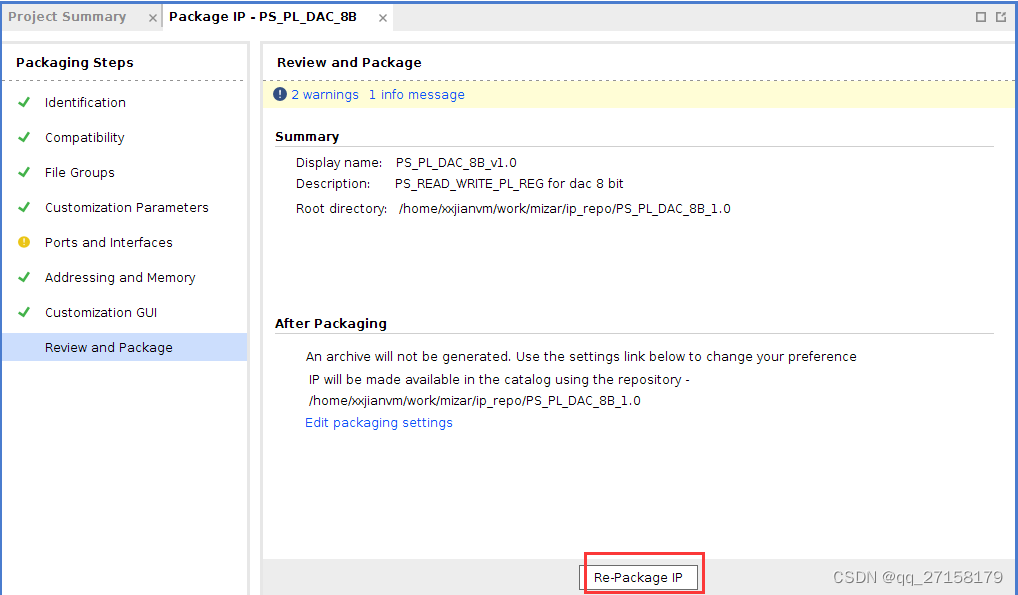

1.2.7 打包

PROJECT MANAGER -> Edit Package IP - PS_PL_DAC_8B ->

-> File Groups -> Merge changes from File Groups Wizard

-> Customization Parameters -> Merge changes from File Groups Wizard

-> Review and Package -> Re-Package IP

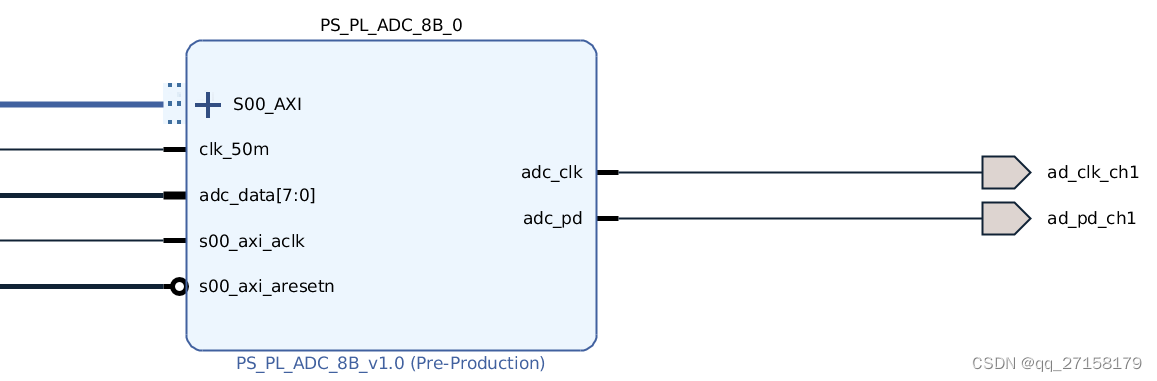

1.3 建立IP- PS_PL_ADC_8B

130个32位的寄存器定义

序号 定义

0 控制1,PS写,采样频率设置

1 控制2,PS写,高16位是采样状态控制,低16位是采样数量

2 回复1,PL写,

3-129 数据,PL写

本程序ADC采样是这样的交互过程:

PS:设置控制2为0001xxxx,空闲

PL:设置回复1为0001xxxx,空闲

PS:设置控制2为0002xxxx,开始采样

PL:设置回复1为0002xxxx,开始采样

PL:设置回复1为0004xxxx,采样完毕

PS:设置控制2为0004xxxx,采样完毕

1.3.1 添加IP

Tools -> Create and Package New IP -> Next

-> Create a new AXI4 peripheral -> Next

-> Name: PS_PL_ADC_8B

-> Description: PS_READ_WRITE_PL_REG for adc 8 bit

-> IP location: /home/xxjianvm/work/mizar/ip_repo

-> Next

-> Add Interface

-> Number of Registers: 130

-> Next

-> Create Peripheral

-> Edit IP -> Finish

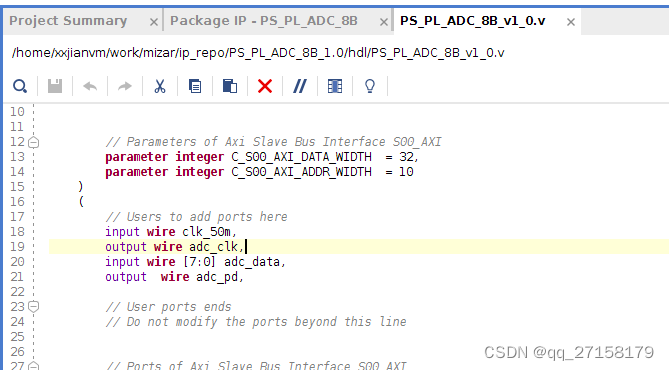

1.3.2 编辑模块端口 PS_PL_ADC_8B_v1_0.v

修改第 17 行

// Users to add ports hereinput wire clk_50m,output wire adc_clk,input wire [7:0] adc_data,output wire adc_pd,// User ports ends

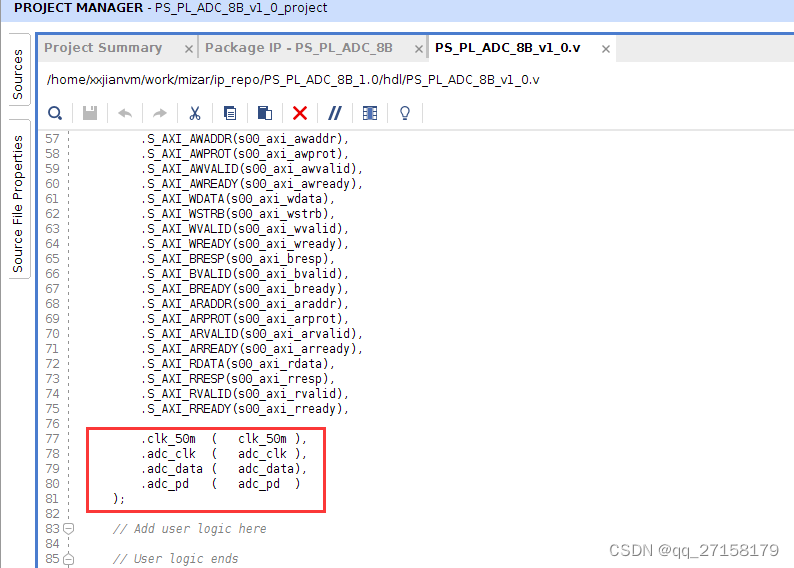

修改第 76 行:

.clk_50m ( clk_50m ),.adc_clk ( adc_clk ),.adc_data ( adc_data),.adc_pd ( adc_pd )

1.3.3 编辑PS_PL_ADC_8B_v1_0_S00_AXI_inst

修改端口,第17行:

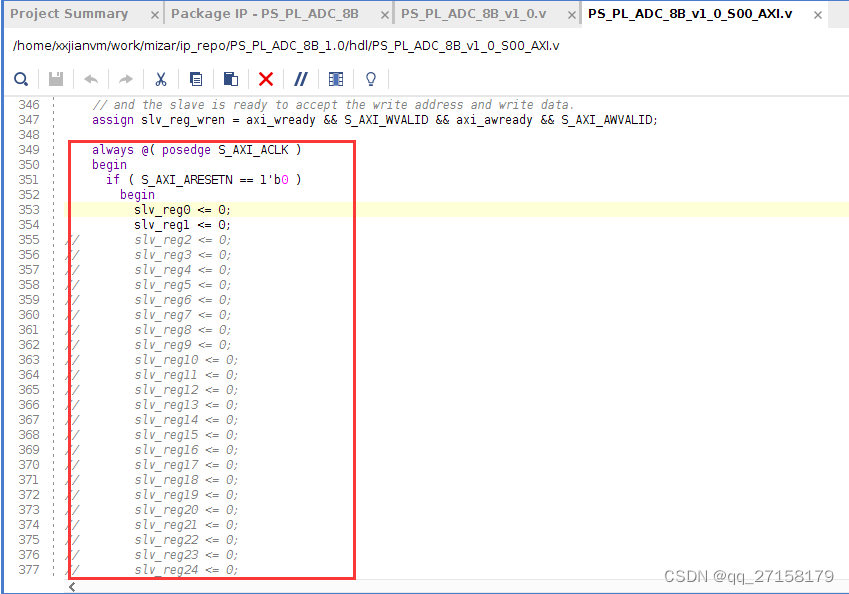

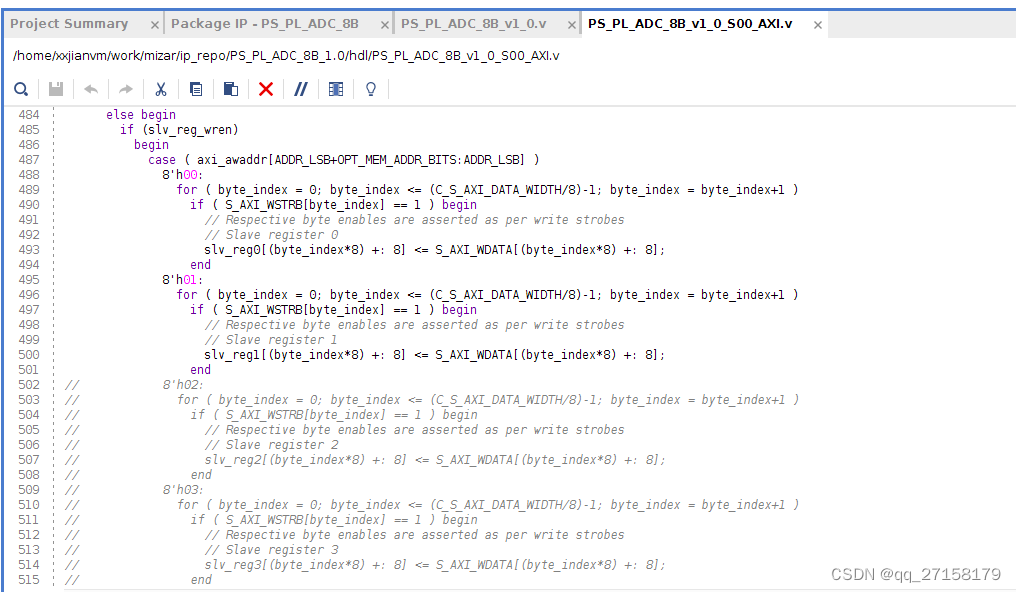

// Users to add ports hereinput wire clk_50m,output wire adc_clk,input wire [7:0] adc_data,output wire adc_pd,// User ports ends把slv_reg2 - slv_reg511改为PL写。

把图示的always模块内的slv_reg2 - slv_reg129 都注释掉,变成PL读写,PS只读。

注释:

// slv_reg2 <= 0;

注释

// slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

注释

// slv_reg2 <= slv_reg2;

注意 slv_reg2 - slv_reg129 都要注释。

1.3.3 编写 clk_div.v

对 50MHz的时钟分频

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 02/18/2024 02:04:13 PM

// Design Name:

// Module Name: clk_div

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module clk_div(clk_50m, rst_n,clk_20m,clk_10m,clk_8m,clk_5m,clk_4m,clk_2m,clk_1m,clk_800k,clk_400k,clk_200k,clk_100k,clk_80k,clk_40k,clk_20k,clk_10k,clk_8k,clk_4k,clk_2k,clk_1k,clk_800,clk_400,clk_200,clk_100);input wire clk_50m;

input wire rst_n;

output wire clk_20m;

output wire clk_10m;

output wire clk_8m;

output wire clk_5m;

output wire clk_4m;

output wire clk_2m;

output wire clk_1m;

output wire clk_800k;

output wire clk_400k;

output wire clk_200k;

output wire clk_100k;

output wire clk_80k;

output wire clk_40k;

output wire clk_20k;

output wire clk_10k;

output wire clk_8k;

output wire clk_4k;

output wire clk_2k;

output wire clk_1k;

output wire clk_800;

output wire clk_400;

output wire clk_200;

output wire clk_100;// 时钟生成模块 20m, 10m, 5m

clk_div2p5 clk_gen_20m(.clk ( clk_50m ),.rstn ( rst_n ) ,.clk_div2p5( clk_20m )

);

clk_div5 clk_gen_10m(.clk ( clk_50m ),.rstn ( rst_n ) ,.clk_div5 ( clk_10m )

);

clk_div10 clk_gen_5m(.clk ( clk_50m ),.rstn ( rst_n ) ,.clk_div10 ( clk_5m )

);// 时钟生成模块 8m, 4m, 2m

clk_div2p5 clk_gen_8m(.clk ( clk_20m ),.rstn ( rst_n ) ,.clk_div2p5( clk_8m )

);

clk_div5 clk_gen_4m(.clk ( clk_20m ),.rstn ( rst_n ) ,.clk_div5 ( clk_4m )

);

clk_div10 clk_gen_2m(.clk ( clk_20m ),.rstn ( rst_n ) ,.clk_div10 ( clk_2m )

);// 时钟生成模块 1m

clk_div10 clk_gen_1m(.clk ( clk_10m ),.rstn ( rst_n ) ,.clk_div10 ( clk_1m )

);

// 时钟生成模块 800k

clk_div2p5 clk_gen_800k(.clk ( clk_2m ),.rstn ( rst_n ) ,.clk_div2p5( clk_800k )

);

// 时钟生成模块 400k, 200k, 100k

clk_div2p5 clk_gen_400k(.clk ( clk_1m ),.rstn ( rst_n ) ,.clk_div2p5( clk_400k )

);

clk_div5 clk_gen_200k(.clk ( clk_1m ),.rstn ( rst_n ) ,.clk_div5 ( clk_200k )

);

clk_div10 clk_gen_100k(.clk ( clk_1m ),.rstn ( rst_n ) ,.clk_div10 ( clk_100k )

);

// 时钟生成模块 80k

clk_div2p5 clk_gen_80k(.clk ( clk_200k ),.rstn ( rst_n ) ,.clk_div2p5( clk_80k )

);

// 时钟生成模块 40k, 20k, 10k

clk_div2p5 clk_gen_40k(.clk ( clk_100k ),.rstn ( rst_n ) ,.clk_div2p5( clk_40k )

);

clk_div5 clk_gen_20k(.clk ( clk_100k ),.rstn ( rst_n ) ,.clk_div5 ( clk_20k )

);

clk_div10 clk_gen_10k(.clk ( clk_100k ),.rstn ( rst_n ) ,.clk_div10 ( clk_10k )

);

// 时钟生成模块 8k, 4k, 2k, 1k

clk_div2p5 clk_gen_8k(.clk ( clk_20k ),.rstn ( rst_n ) ,.clk_div2p5( clk_8k )

);

clk_div2p5 clk_gen_4k(.clk ( clk_10k ),.rstn ( rst_n ) ,.clk_div2p5( clk_4k )

);

clk_div5 clk_gen_2k(.clk ( clk_10k ),.rstn ( rst_n ) ,.clk_div5 ( clk_2k )

);

clk_div10 clk_gen_1k(.clk ( clk_10k ),.rstn ( rst_n ) ,.clk_div10 ( clk_1k )

);

// 时钟生成模块 800, 400, 200, 100

clk_div2p5 clk_gen_800(.clk ( clk_2k ),.rstn ( rst_n ) ,.clk_div2p5( clk_800 )

);

clk_div2p5 clk_gen_400(.clk ( clk_1k ),.rstn ( rst_n ) ,.clk_div2p5( clk_400 )

);

clk_div5 clk_gen_200(.clk ( clk_1k ),.rstn ( rst_n ) ,.clk_div5 ( clk_200 )

);

clk_div10 clk_gen_100(.clk ( clk_1k ),.rstn ( rst_n ) ,.clk_div10 ( clk_100 )

);

endmodule

1.3.4 编写 adc_clk_drv.v

根据 寄存器0 slv_reg0,设置ADC时钟

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 02/18/2024 02:31:22 PM

// Design Name:

// Module Name: adc_clk

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module adc_clk(clk_50m, rst_n, slv_reg0,adc_clk);input wire clk_50m;

input wire rst_n;

input wire [31:0] slv_reg0;

output wire adc_clk; reg adc_clk_r;

wire clk_20m;

wire clk_10m;

wire clk_8m;

wire clk_5m;

wire clk_4m;

wire clk_2m;

wire clk_1m;

wire clk_800k;

wire clk_400k;

wire clk_200k;

wire clk_100k;

wire clk_80k;

wire clk_40k;

wire clk_20k;

wire clk_10k;

wire clk_8k;

wire clk_4k;

wire clk_2k;

wire clk_1k;

wire clk_800;

wire clk_400;

wire clk_200;

wire clk_100;clk_div clk_gen(.clk_50m ( clk_50m ), .rst_n ( rst_n ),.clk_20m ( clk_20m ),.clk_10m ( clk_10m ),.clk_8m ( clk_8m ),.clk_5m ( clk_5m ),.clk_4m ( clk_4m ),.clk_2m ( clk_2m ),.clk_1m ( clk_1m ),.clk_800k ( clk_800k),.clk_400k ( clk_400k),.clk_200k ( clk_200k),.clk_100k ( clk_100k),.clk_80k ( clk_80k ),.clk_40k ( clk_40k ),.clk_20k ( clk_20k ),.clk_10k ( clk_10k ),.clk_8k ( clk_8k ),.clk_4k ( clk_4k ),.clk_2k ( clk_2k ),.clk_1k ( clk_1k ),.clk_800 ( clk_800 ),.clk_400 ( clk_400 ),.clk_200 ( clk_200 ),.clk_100 ( clk_100 ));always @( posedge clk_50m or negedge rst_n ) beginif( ~rst_n ) beginadc_clk_r <= 1'b0;endelse beginif ( slv_reg0 >= 32'd20_000_000 ) beginadc_clk_r <= clk_20m;endelse if ( slv_reg0 >= 32'd10_000_000 ) beginadc_clk_r <= clk_10m;endelse if ( slv_reg0 >= 32'd8_000_000 ) beginadc_clk_r <= clk_8m;endelse if ( slv_reg0 >= 32'd5_000_000 ) beginadc_clk_r <= clk_5m;endelse if ( slv_reg0 >= 32'd4_000_000 ) beginadc_clk_r <= clk_4m;endelse if ( slv_reg0 >= 32'd2_000_000 ) beginadc_clk_r <= clk_2m;endelse if ( slv_reg0 >= 32'd1_000_000 ) beginadc_clk_r <= clk_1m;endelse if ( slv_reg0 >= 32'd800_000 ) beginadc_clk_r <= clk_800k;endelse if ( slv_reg0 >= 32'd400_000 ) beginadc_clk_r <= clk_400k;endelse if ( slv_reg0 >= 32'd200_000 ) beginadc_clk_r <= clk_200k;endelse if ( slv_reg0 >= 32'd100_000 ) beginadc_clk_r <= clk_100k;endelse if ( slv_reg0 >= 32'd80_000 ) beginadc_clk_r <= clk_80k;endelse if ( slv_reg0 >= 32'd40_000 ) beginadc_clk_r <= clk_40k;endelse if ( slv_reg0 >= 32'd20_000 ) beginadc_clk_r <= clk_20k;endelse if ( slv_reg0 >= 32'd10_000 ) beginadc_clk_r <= clk_10k;endelse if ( slv_reg0 >= 32'd8_000 ) beginadc_clk_r <= clk_8k;endelse if ( slv_reg0 >= 32'd4_000 ) beginadc_clk_r <= clk_4k;endelse if ( slv_reg0 >= 32'd2_000 ) beginadc_clk_r <= clk_2k;endelse if ( slv_reg0 >= 32'd1_000 ) beginadc_clk_r <= clk_1k;endelse if ( slv_reg0 >= 32'd800 ) beginadc_clk_r <= clk_800;endelse if ( slv_reg0 >= 32'd400 ) beginadc_clk_r <= clk_400;endelse if ( slv_reg0 >= 32'd200 ) beginadc_clk_r <= clk_200;endelse if ( slv_reg0 >= 32'd100 ) beginadc_clk_r <= clk_100;endelse beginadc_clk_r <= clk_1m;//adc_clk_r <= 1'b0;endend

end

//assign adc_clk = adc_clk_r ? 1:0;

assign adc_clk = adc_clk_r;endmodule

1.3.5 编辑 PS_PL_ADC_8B_v1_0_S00_AXI.v

实现ADC控制的相关逻辑。这里直接放出源码。

`timescale 1 ns / 1 psmodule PS_PL_ADC_8B_v1_0_S00_AXI #(// Users to add parameters here// User parameters ends// Do not modify the parameters beyond this line// Width of S_AXI data busparameter integer C_S_AXI_DATA_WIDTH = 32,// Width of S_AXI address busparameter integer C_S_AXI_ADDR_WIDTH = 10)(// Users to add ports hereinput wire clk_50m,output wire adc_clk,input wire [7:0] adc_data,output wire adc_pd,// User ports ends// Do not modify the ports beyond this line// Global Clock Signalinput wire S_AXI_ACLK,// Global Reset Signal. This Signal is Active LOWinput wire S_AXI_ARESETN,// Write address (issued by master, acceped by Slave)input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_AWADDR,// Write channel Protection type. This signal indicates the// privilege and security level of the transaction, and whether// the transaction is a data access or an instruction access.input wire [2 : 0] S_AXI_AWPROT,// Write address valid. This signal indicates that the master signaling// valid write address and control information.input wire S_AXI_AWVALID,// Write address ready. This signal indicates that the slave is ready// to accept an address and associated control signals.output wire S_AXI_AWREADY,// Write data (issued by master, acceped by Slave) input wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_WDATA,// Write strobes. This signal indicates which byte lanes hold// valid data. There is one write strobe bit for each eight// bits of the write data bus. input wire [(C_S_AXI_DATA_WIDTH/8)-1 : 0] S_AXI_WSTRB,// Write valid. This signal indicates that valid write// data and strobes are available.input wire S_AXI_WVALID,// Write ready. This signal indicates that the slave// can accept the write data.output wire S_AXI_WREADY,// Write response. This signal indicates the status// of the write transaction.output wire [1 : 0] S_AXI_BRESP,// Write response valid. This signal indicates that the channel// is signaling a valid write response.output wire S_AXI_BVALID,// Response ready. This signal indicates that the master// can accept a write response.input wire S_AXI_BREADY,// Read address (issued by master, acceped by Slave)input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_ARADDR,// Protection type. This signal indicates the privilege// and security level of the transaction, and whether the// transaction is a data access or an instruction access.input wire [2 : 0] S_AXI_ARPROT,// Read address valid. This signal indicates that the channel// is signaling valid read address and control information.input wire S_AXI_ARVALID,// Read address ready. This signal indicates that the slave is// ready to accept an address and associated control signals.output wire S_AXI_ARREADY,// Read data (issued by slave)output wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_RDATA,// Read response. This signal indicates the status of the// read transfer.output wire [1 : 0] S_AXI_RRESP,// Read valid. This signal indicates that the channel is// signaling the required read data.output wire S_AXI_RVALID,// Read ready. This signal indicates that the master can// accept the read data and response information.input wire S_AXI_RREADY);// AXI4LITE signalsreg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_awaddr;reg axi_awready;reg axi_wready;reg [1 : 0] axi_bresp;reg axi_bvalid;reg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_araddr;reg axi_arready;reg [C_S_AXI_DATA_WIDTH-1 : 0] axi_rdata;reg [1 : 0] axi_rresp;reg axi_rvalid;// Example-specific design signals// local parameter for addressing 32 bit / 64 bit C_S_AXI_DATA_WIDTH// ADDR_LSB is used for addressing 32/64 bit registers/memories// ADDR_LSB = 2 for 32 bits (n downto 2)// ADDR_LSB = 3 for 64 bits (n downto 3)localparam integer ADDR_LSB = (C_S_AXI_DATA_WIDTH/32) + 1;localparam integer OPT_MEM_ADDR_BITS = 7;//----------------------------------------------//-- Signals for user logic register space example//------------------------------------------------//-- Number of Slave Registers 130reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg0;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg1;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg2;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg3;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg4;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg5;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg6;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg7;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg8;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg9;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg10;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg11;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg12;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg13;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg14;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg15;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg16;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg17;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg18;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg19;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg20;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg21;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg22;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg23;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg24;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg25;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg26;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg27;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg28;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg29;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg30;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg31;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg32;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg33;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg34;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg35;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg36;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg37;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg38;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg39;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg40;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg41;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg42;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg43;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg44;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg45;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg46;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg47;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg48;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg49;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg50;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg51;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg52;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg53;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg54;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg55;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg56;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg57;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg58;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg59;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg60;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg61;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg62;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg63;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg64;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg65;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg66;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg67;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg68;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg69;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg70;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg71;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg72;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg73;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg74;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg75;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg76;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg77;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg78;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg79;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg80;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg81;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg82;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg83;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg84;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg85;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg86;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg87;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg88;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg89;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg90;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg91;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg92;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg93;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg94;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg95;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg96;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg97;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg98;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg99;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg100;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg101;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg102;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg103;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg104;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg105;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg106;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg107;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg108;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg109;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg110;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg111;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg112;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg113;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg114;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg115;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg116;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg117;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg118;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg119;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg120;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg121;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg122;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg123;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg124;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg125;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg126;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg127;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg128;reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg129;wire slv_reg_rden;wire slv_reg_wren;reg [C_S_AXI_DATA_WIDTH-1:0] reg_data_out;integer byte_index;reg aw_en;// I/O Connections assignmentsassign S_AXI_AWREADY = axi_awready;assign S_AXI_WREADY = axi_wready;assign S_AXI_BRESP = axi_bresp;assign S_AXI_BVALID = axi_bvalid;assign S_AXI_ARREADY = axi_arready;assign S_AXI_RDATA = axi_rdata;assign S_AXI_RRESP = axi_rresp;assign S_AXI_RVALID = axi_rvalid;// Implement axi_awready generation// axi_awready is asserted for one S_AXI_ACLK clock cycle when both// S_AXI_AWVALID and S_AXI_WVALID are asserted. axi_awready is// de-asserted when reset is low.always @( posedge S_AXI_ACLK )beginif ( S_AXI_ARESETN == 1'b0 )beginaxi_awready <= 1'b0;aw_en <= 1'b1;end elsebegin if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)begin// slave is ready to accept write address when // there is a valid write address and write data// on the write address and data bus. This design // expects no outstanding transactions. axi_awready <= 1'b1;aw_en <= 1'b0;endelse if (S_AXI_BREADY && axi_bvalid)beginaw_en <= 1'b1;axi_awready <= 1'b0;endelse beginaxi_awready <= 1'b0;endend end // Implement axi_awaddr latching// This process is used to latch the address when both // S_AXI_AWVALID and S_AXI_WVALID are valid. always @( posedge S_AXI_ACLK )beginif ( S_AXI_ARESETN == 1'b0 )beginaxi_awaddr <= 0;end elsebegin if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)begin// Write Address latching axi_awaddr <= S_AXI_AWADDR;endend end // Implement axi_wready generation// axi_wready is asserted for one S_AXI_ACLK clock cycle when both// S_AXI_AWVALID and S_AXI_WVALID are asserted. axi_wready is // de-asserted when reset is low. always @( posedge S_AXI_ACLK )beginif ( S_AXI_ARESETN == 1'b0 )beginaxi_wready <= 1'b0;end elsebegin if (~axi_wready && S_AXI_WVALID && S_AXI_AWVALID && aw_en )begin// slave is ready to accept write data when // there is a valid write address and write data// on the write address and data bus. This design // expects no outstanding transactions. axi_wready <= 1'b1;endelsebeginaxi_wready <= 1'b0;endend end // Implement memory mapped register select and write logic generation// The write data is accepted and written to memory mapped registers when// axi_awready, S_AXI_WVALID, axi_wready and S_AXI_WVALID are asserted. Write strobes are used to// select byte enables of slave registers while writing.// These registers are cleared when reset (active low) is applied.// Slave register write enable is asserted when valid address and data are available// and the slave is ready to accept the write address and write data.assign slv_reg_wren = axi_wready && S_AXI_WVALID && axi_awready && S_AXI_AWVALID;always @( posedge S_AXI_ACLK )beginif ( S_AXI_ARESETN == 1'b0 )beginslv_reg0 <= 0;slv_reg1 <= 0;

// slv_reg2 <= 0;

// slv_reg3 <= 0;

// slv_reg4 <= 0;

// slv_reg5 <= 0;

// slv_reg6 <= 0;

// slv_reg7 <= 0;

// slv_reg8 <= 0;

// slv_reg9 <= 0;

// slv_reg10 <= 0;

// slv_reg11 <= 0;

// slv_reg12 <= 0;

// slv_reg13 <= 0;

// slv_reg14 <= 0;

// slv_reg15 <= 0;

// slv_reg16 <= 0;

// slv_reg17 <= 0;

// slv_reg18 <= 0;

// slv_reg19 <= 0;

// slv_reg20 <= 0;

// slv_reg21 <= 0;

// slv_reg22 <= 0;

// slv_reg23 <= 0;

// slv_reg24 <= 0;

// slv_reg25 <= 0;

// slv_reg26 <= 0;

// slv_reg27 <= 0;

// slv_reg28 <= 0;

// slv_reg29 <= 0;

// slv_reg30 <= 0;

// slv_reg31 <= 0;

// slv_reg32 <= 0;

// slv_reg33 <= 0;

// slv_reg34 <= 0;

// slv_reg35 <= 0;

// slv_reg36 <= 0;

// slv_reg37 <= 0;

// slv_reg38 <= 0;

// slv_reg39 <= 0;

// slv_reg40 <= 0;

// slv_reg41 <= 0;

// slv_reg42 <= 0;

// slv_reg43 <= 0;

// slv_reg44 <= 0;

// slv_reg45 <= 0;

// slv_reg46 <= 0;

// slv_reg47 <= 0;

// slv_reg48 <= 0;

// slv_reg49 <= 0;

// slv_reg50 <= 0;

// slv_reg51 <= 0;

// slv_reg52 <= 0;

// slv_reg53 <= 0;

// slv_reg54 <= 0;

// slv_reg55 <= 0;

// slv_reg56 <= 0;

// slv_reg57 <= 0;

// slv_reg58 <= 0;

// slv_reg59 <= 0;

// slv_reg60 <= 0;

// slv_reg61 <= 0;

// slv_reg62 <= 0;

// slv_reg63 <= 0;

// slv_reg64 <= 0;

// slv_reg65 <= 0;

// slv_reg66 <= 0;

// slv_reg67 <= 0;

// slv_reg68 <= 0;

// slv_reg69 <= 0;

// slv_reg70 <= 0;

// slv_reg71 <= 0;

// slv_reg72 <= 0;

// slv_reg73 <= 0;

// slv_reg74 <= 0;

// slv_reg75 <= 0;

// slv_reg76 <= 0;

// slv_reg77 <= 0;

// slv_reg78 <= 0;

// slv_reg79 <= 0;

// slv_reg80 <= 0;

// slv_reg81 <= 0;

// slv_reg82 <= 0;

// slv_reg83 <= 0;

// slv_reg84 <= 0;

// slv_reg85 <= 0;

// slv_reg86 <= 0;

// slv_reg87 <= 0;

// slv_reg88 <= 0;

// slv_reg89 <= 0;

// slv_reg90 <= 0;

// slv_reg91 <= 0;

// slv_reg92 <= 0;

// slv_reg93 <= 0;

// slv_reg94 <= 0;

// slv_reg95 <= 0;

// slv_reg96 <= 0;

// slv_reg97 <= 0;

// slv_reg98 <= 0;

// slv_reg99 <= 0;

// slv_reg100 <= 0;

// slv_reg101 <= 0;

// slv_reg102 <= 0;

// slv_reg103 <= 0;

// slv_reg104 <= 0;

// slv_reg105 <= 0;

// slv_reg106 <= 0;

// slv_reg107 <= 0;

// slv_reg108 <= 0;

// slv_reg109 <= 0;

// slv_reg110 <= 0;

// slv_reg111 <= 0;

// slv_reg112 <= 0;

// slv_reg113 <= 0;

// slv_reg114 <= 0;

// slv_reg115 <= 0;

// slv_reg116 <= 0;

// slv_reg117 <= 0;

// slv_reg118 <= 0;

// slv_reg119 <= 0;

// slv_reg120 <= 0;

// slv_reg121 <= 0;

// slv_reg122 <= 0;

// slv_reg123 <= 0;

// slv_reg124 <= 0;

// slv_reg125 <= 0;

// slv_reg126 <= 0;

// slv_reg127 <= 0;

// slv_reg128 <= 0;

// slv_reg129 <= 0;end else beginif (slv_reg_wren)begincase ( axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )8'h00:for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )if ( S_AXI_WSTRB[byte_index] == 1 ) begin// Respective byte enables are asserted as per write strobes // Slave register 0slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];end 8'h01:for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )if ( S_AXI_WSTRB[byte_index] == 1 ) begin// Respective byte enables are asserted as per write strobes // Slave register 1slv_reg1[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];end

// 8'h02:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 2

// slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h03:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 3

// slv_reg3[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h04:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 4

// slv_reg4[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h05:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 5

// slv_reg5[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h06:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 6

// slv_reg6[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h07:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 7

// slv_reg7[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h08:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 8

// slv_reg8[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h09:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 9

// slv_reg9[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0A:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 10

// slv_reg10[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0B:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 11

// slv_reg11[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0C:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 12

// slv_reg12[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0D:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 13

// slv_reg13[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0E:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 14

// slv_reg14[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h0F:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 15

// slv_reg15[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h10:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 16

// slv_reg16[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h11:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 17

// slv_reg17[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h12:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 18

// slv_reg18[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h13:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 19

// slv_reg19[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h14:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 20

// slv_reg20[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h15:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 21

// slv_reg21[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h16:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 22

// slv_reg22[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h17:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 23

// slv_reg23[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h18:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 24

// slv_reg24[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h19:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 25

// slv_reg25[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1A:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 26

// slv_reg26[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1B:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 27

// slv_reg27[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1C:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 28

// slv_reg28[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1D:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 29

// slv_reg29[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1E:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 30

// slv_reg30[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h1F:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 31

// slv_reg31[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h20:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 32

// slv_reg32[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h21:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 33

// slv_reg33[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h22:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 34

// slv_reg34[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h23:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 35

// slv_reg35[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h24:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 36

// slv_reg36[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h25:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 37

// slv_reg37[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h26:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 38

// slv_reg38[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h27:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 39

// slv_reg39[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h28:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 40

// slv_reg40[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h29:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 41

// slv_reg41[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h2A:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 42

// slv_reg42[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h2B:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// // Respective byte enables are asserted as per write strobes

// // Slave register 43

// slv_reg43[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

// end

// 8'h2C:

// for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

// if ( S_AXI_WSTRB[byte_index] == 1 ) begin