原文:RISC-V Moving Toward Open Server Specification

作者:Agam Shah

转载自:https://www.hpcwire.com/2023/07/24/risc-v-moving-toward-open-server-specification/

中文翻译:

2023年7月24日

RISC-V International目前正在起草一份可以标准化RISC-V服务器芯片和系统开发的规范,RISC-V International是一个处理指令集架构开发的组织。

该规范为基于RISC-V技术的各层服务器计算系统建立了标准接口。它可以帮助公司在云计算环境中部署RISC-V服务器,其中软件通过虚拟化CPU运行,而不是直接从硬件CPU运行。

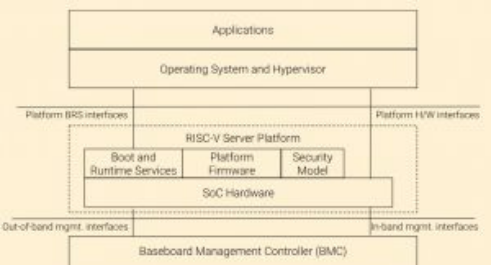

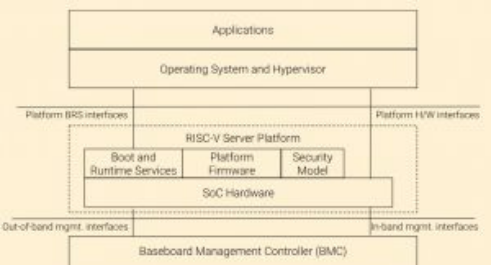

可以肯定的是,服务器规格还处于早期阶段。当前的迭代包括系统管理控制器、片上系统模块、安全层、引导系统和虚拟化层。

RISC-V在一份定义该规范的文件中表示:“RISC-V服务器SoC(片上系统)规范定义了一套标准化的功能,便携式系统软件(如操作系统和虚拟机管理程序)可以依赖这些功能存在于RISC-V服务器SoC中。”此处提供规范链接。

RISC-V是一个可免费许可的指令集架构。任何人都可以根据架构创建芯片,但公司也可以添加其专有模块并出售这些芯片。RISC-V得到了大多数顶级芯片制造商的支持,包括英特尔、AMD、苹果、英伟达和高通。

开放计算项目还定义了x86和ARM服务器的类似规格,这些规格被服务器制造商用作构建标准化数据中心产品的蓝图。

RISC-V提案还为服务器系统提供了基础,以支持CXL等技术,CXL已经得到了x86和ARM服务器制造商的支持。

即将推出的CXL 3.0规范在芯片、内存和存储之间提供了高速通信链路,并引起了服务器硬件制造商的兴趣,因为它可能会改变数据中心的构建方式。该规范将通过分解计算和存储模块来减少处理和带宽阻塞点。

服务器规范建立在指令集架构技术之上,例如近年来批准的较新的矢量处理规范。

许多RISC-V公司正在构建服务器芯片,其中最著名的是Ventana和Esperanto。

这些公司在基本指令集架构之上构建了自己的专有模块,但表示他们将标准化为RISC-V International批准的最新规格。

欧洲和美国的研究机构正在试验RISC-V微服务器来开发和测试软件。

创建服务器规范的提案也反映了RISC-V的开源精神——作为一个社区共同开发和改进产品。

RISC-V International的首席技术官Mark Himelstein在上个月在巴塞罗那举行的RISC-V峰会上发表演讲时说:“我们之所以是一个社区......是因为我们可以分担负担。”

目标是防止RISC-V社区中的硬件和软件碎片化。RISC-V International希望避免Android的命运,随着手机开发人员修改操作系统以满足他们的智能手机需求,Android的命运迅速支离破碎。

“我们分担定义ISA的工作,我们分担寻找硬件-软件接口的工作......我们分担软件负担。从引导代码到应用程序,它意味着一切,”Himelstein说。

RISC-V仍然不被认为是主导数据中心市场的x86或ARM的可行服务器替代品。

“当人们说'哦,RISC 5落后ARM10年'时,答案是肯定的,但不需要10年就能赶上。世界语系统首席执行官Dave Ditzel在RISC-V峰会的另一场演讲中说:“需要几年时间才能赶上。”

英语原文:

July 24, 2023

A specification that could standardize the development of RISC-V server chips and systems is currently being drafted by RISC-V International, an organization that is handling the development of the instruction set architecture.

The specification establishes standard interfaces for various layers of server computing systems built on RISC-V technology. It could help companies deploy RISC-V servers in cloud computing environments, in which software runs off virtualized CPUs and not directly off hardware CPUs.

To be sure, the server spec is in its early stages. The current iteration includes system management controllers, system-on-chip modules, security layers, boot systems, and virtualization layers.

“The RISC-V server SoC (system on chip) specification defines a standardized set of capabilities that portable system software such as operating systems and hypervisors can rely on being present in a RISC-V server SoC,” RISC-V said in a document defining the specification. A link to the specification is availablehere.

RISC-V is an instruction-set architecture that is free to license. Anyone can create chips based on the architecture, but companies can also add their proprietary modules and sell those chips. RISC-V is backed by most of the top chipmakers, including Intel, AMD, Apple, Nvidia, and Qualcomm.

The Open Compute Project has also defined similar specs for x86 and ARM servers, which are used as blueprints by server makers to build standardized data-center products.

The RISC-V proposal also provides a base for server systems to support technologies like CXL, which is already backed by x86 and ARM server makers.

The upcoming CXL 3.0 spec provides a high-speed communication link between chips, memory, and storage, and is drawing interest from server hardware makers as it could change the way data centers are built. The spec will cut processing and bandwidth chokepoints by disaggregating compute and storage modules.

The server spec is built on top of technologies in the instruction set architecture such as the newer vector processing specification, which has been ratified in recent years.

Many RISC-V companies are building server chips, with the most notable being Ventana and Esperanto.

The companies have built their own proprietary modules on top of the base instruction set architecture but have said they would standardize to the latest specs ratified by RISC-V International.

Research organizations in the Europe and U.S. are experimenting with RISC-V microservers to develop and test software.

The proposal to create a server spec also reflects the open-source ethos of RISC-V — to jointly develop and improve a product as a community.

“The reason we’re a community at all…is we get to share the burden,” said Mark Himelstein, the chief technology officer at RISC-V International, during a recent presentation at a RISC-V Summit held last month in Barcelona.

The goal is to prevent hardware and software fragmentation in the RISC-V community. RISC-V International wants to avoid the fate of Android, which quickly fragmented as phone developers modified the OS to meet their smartphone needs.

“We share the work of defining the ISA, we share the work of finding the hardware-software interface… and we share the software burden. It means everything from boot code all the way up to applications,” Himelstein said.

RISC-V still is not considered a viable server alternative to x86 or ARM, which dominate the data center market.

“When people say ‘Oh, RISC five is 10 years behind ARM,’ the answer is yes, but it is not going to take 10 years to catch up. It will take a couple of years to catch up,” said Dave Ditzel, CEO of Esperanto Systems, during another presentation at the RISC-V Summit.

-

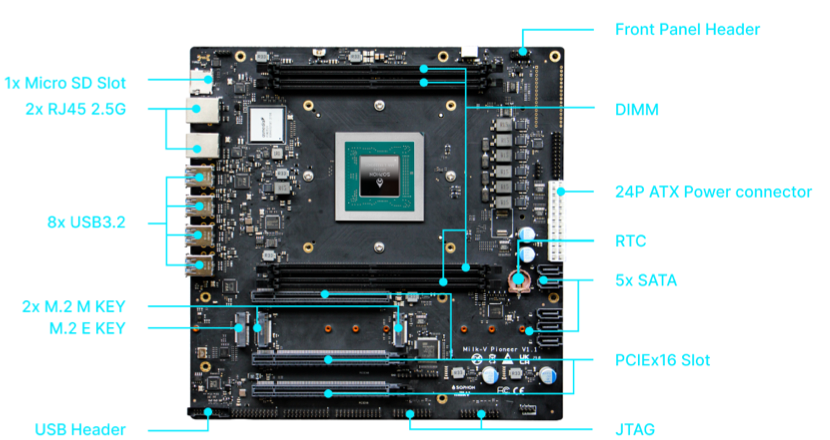

About HS-2

HS-2 RISC-V通用主板是澎峰科技与合作伙伴共同研发的一款专为开发者设计的标准mATX主板,它预装了澎峰科技为RISC-V高性能服务器定制开发的软件包,包括各种标准bencmark、支持V扩展

的GCC编译器、计算库、中间件以及多种典型服务器应用程序。

HS-2 RISC-V通用主板搭载了一颗国产RISC-V 64核处理器(SG2042)。SG2042是目前已量产的性能最高的RISC-V处理器,主要针对高性能计算领域需求设计,适用于科学计算、工程计算、AI计算、融合计算等大算力应用场景。