目录

1. AXI总线概述

1.1 主要特点

1.2 通道功能

1.3 信号概览

2. AXI Interconnect

2.1 信号说明

2.2 内部结构

3. PS-PL AXI Interface

3.1 AXI FPD/LFP/ACP

3.2 Address Editor

3.3 地址空间

3.4 AXI-DDR

4. 通过ILA观察AXI信号

4.1 AXI 读通道

1. AXI总线概述

AXI(Advanced eXtensible Interface)总线是ARM公司在AMBA 3.0协议中提出的一个重要部分,主要面向高性能、高带宽、低延迟的片内总线设计。在AMBA 4.0版本中,AXI被进一步发展为AXI4,包括AXI4、AXI4-Lite、AXI4-Stream等多个版本。

1.1 主要特点

高性能和高频率系统设计:AXI协议支持高带宽和低延时设计,适合于需要高频操作的系统。

读写通道分离:AXI协议定义了五个独立的传输通道,包括读地址通道、读数据通道、写地址通道、写数据通道和写响应通道,从而支持全双工的数据传输。

灵活的互联架构:AXI提供了单一的接口定义,适用于master/interconnect、slave/interconnect和master/slave之间的连接。

支持多种传输类型:包括burst传输、乱序传输和outstanding传输,有助于提高数据处理效率。

易于时序收敛:AXI协议允许在任何通道的任何点插入寄存器级,以实现时序收敛。

1.2 通道功能

读地址通道(Read Address Channel):携带读操作的地址和控制信息。

读数据通道(Read Data Channel):用于从slave到master的数据传输。

写地址通道(Write Address Channel):携带写操作的地址和控制信息。

写数据通道(Write Data Channel):用于从master到slave的数据传输。

写响应通道(Write Response Channel):用于slave对写操作的响应。

1.3 信号概览

2. AXI Interconnect

AXI Interconnect 非常常见。它用于连接多个AXI主设备和从设备的关键组件。它是ARM AMBA规范的一部分,专门设计来处理多个主设备和从设备之间的通信。

AXI Interconnect 一般由Vivado自动生成并连接。理解其作用有助于提到系统设计能力。

2.1 信号说明

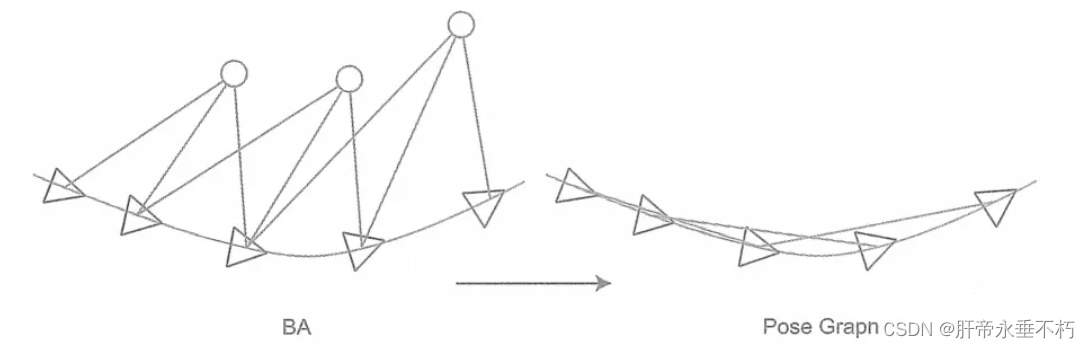

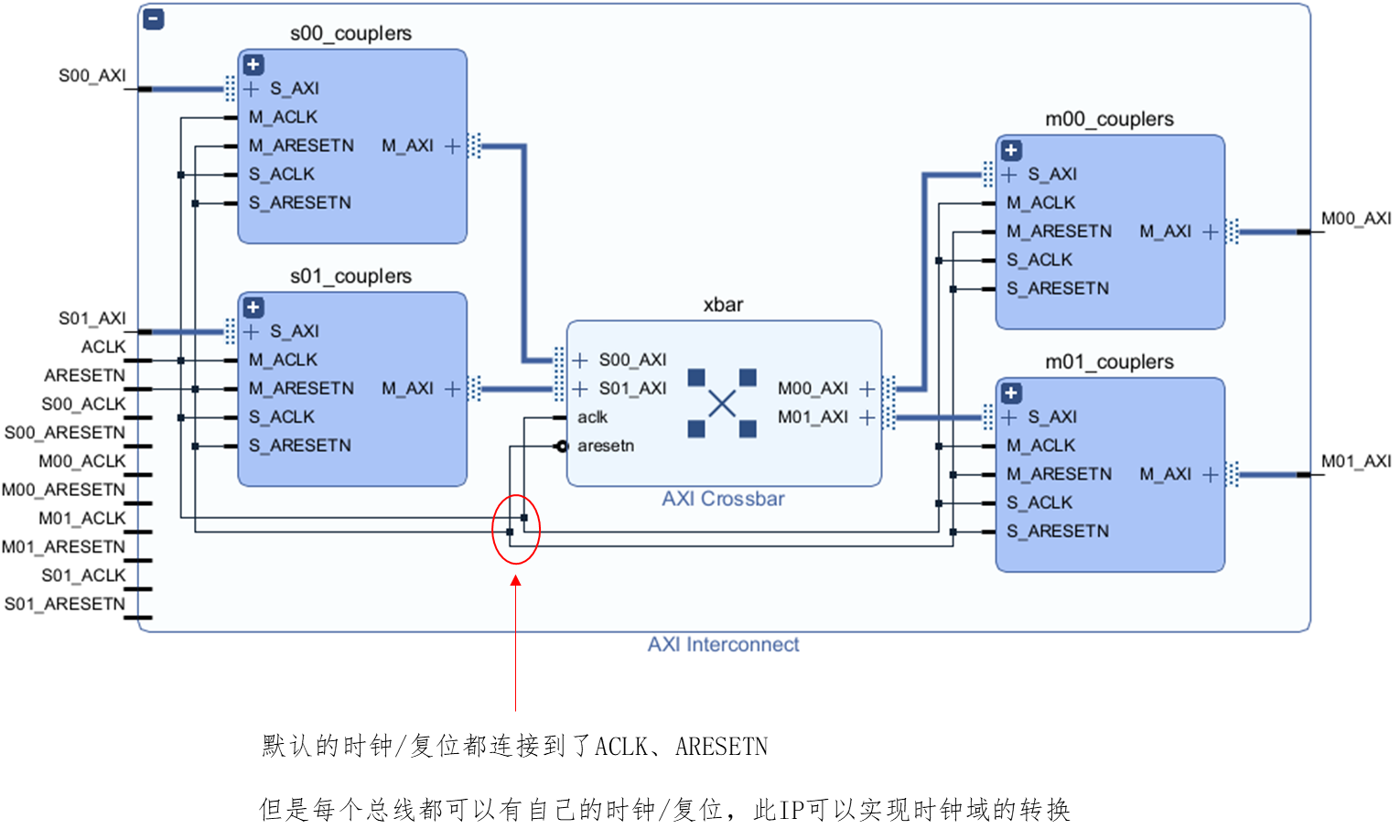

2.2 内部结构

当任何连接的主设备或从设备的接口特性与互联内部的交叉开关不同时,适当的基础架构核心会被自动推断和连接到互联中执行必要的转换:

AXI Crossbar(交叉开关):将一个或多个相似的AXI内存映射主设备连接到一个或多个相似的内存映射从设备。

AXI Data Width Converter(数据宽度转换器):将一个AXI内存映射主设备连接到一个具有更宽或更窄数据通道的AXI内存映射从设备。

AXI Clock Converter(时钟转换器):将一个AXI内存映射主设备连接到一个在不同时钟域中操作的AXI内存映射从设备。

AXI Clock Converter(时钟转换器):将一个AXI内存映射主设备连接到一个在不同时钟域中操作的AXI内存映射从设备。

AXI Protocol Converter(协议转换器):将一个AXI4、AXI3或AXI4-Lite主设备连接到一个不同的AXI内存映射协议的AXI从设备。

AXI Data FIFO(数据FIFO):通过一组FIFO缓冲器将一个AXI内存映射主设备连接到一个AXI内存映射从设备。

AXI Register Slice(寄存器切片):通过一组流水线寄存器将一个AXI内存映射主设备连接到一个AXI内存映射从设备,通常用于打破关键时序路径。

AXI MMU(内存映射单元):为AXI互联提供地址范围解码和重映射服务。

3. PS-PL AXI Interface

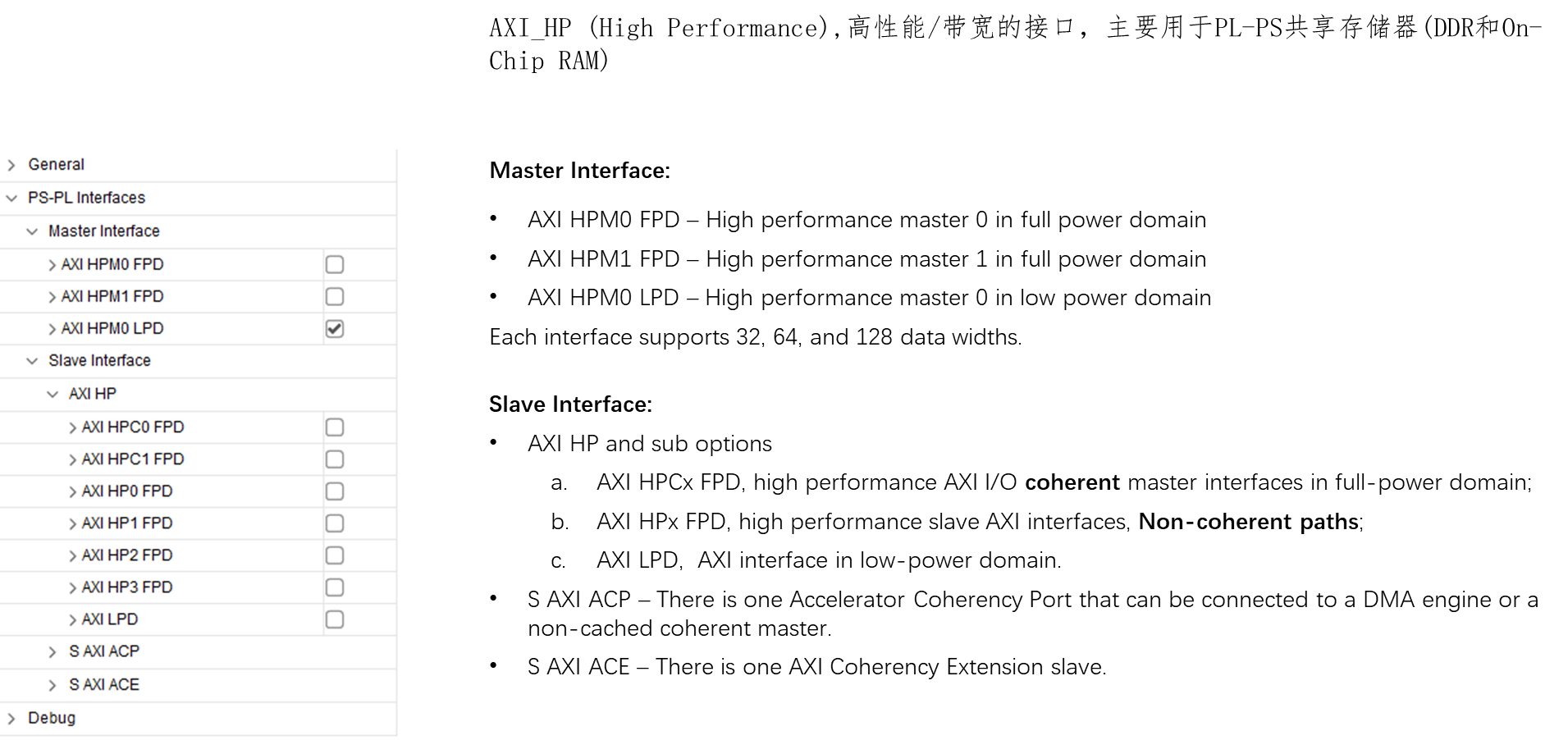

3.1 AXI FPD/LFP/ACP

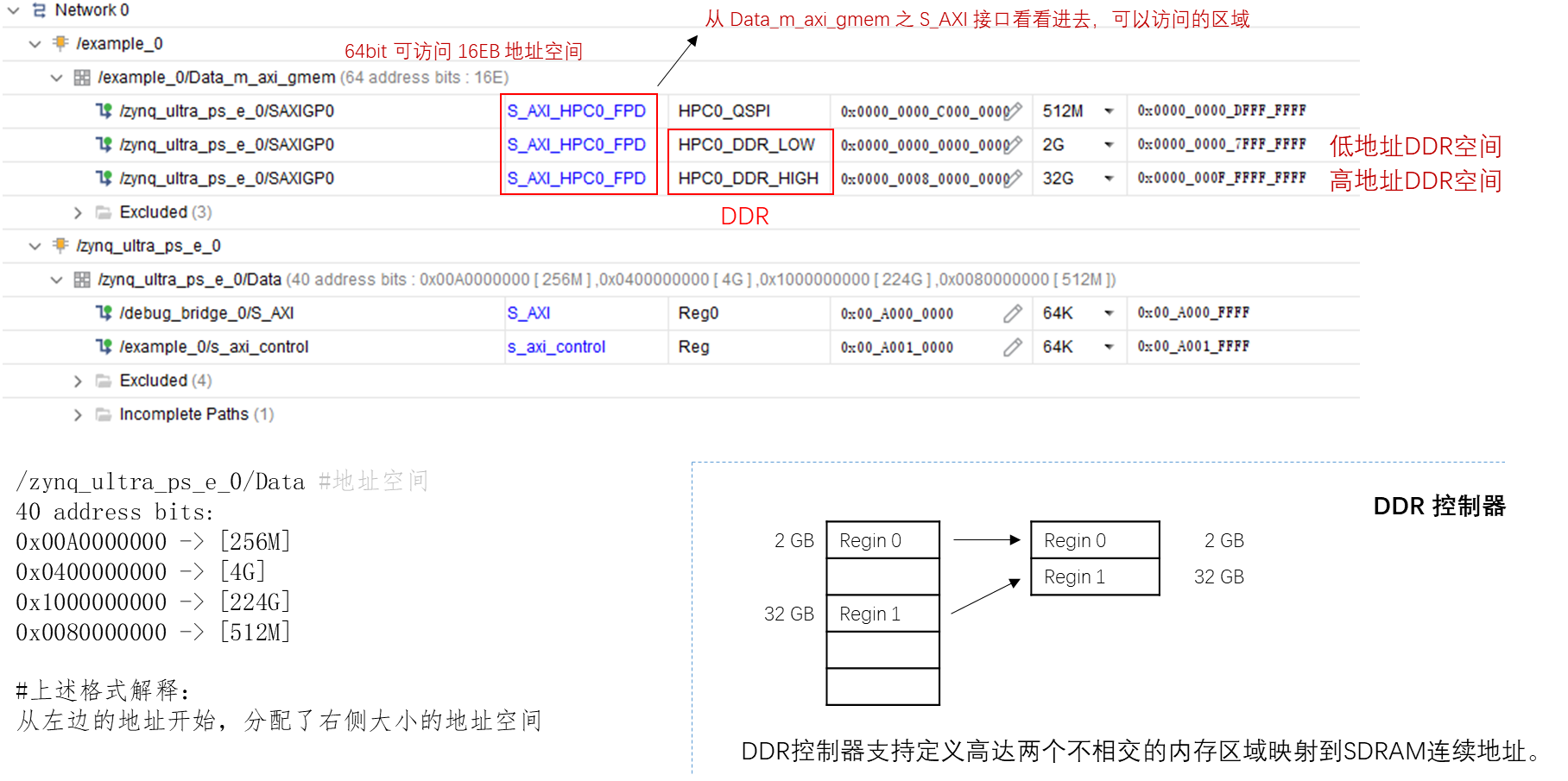

3.2 Address Editor

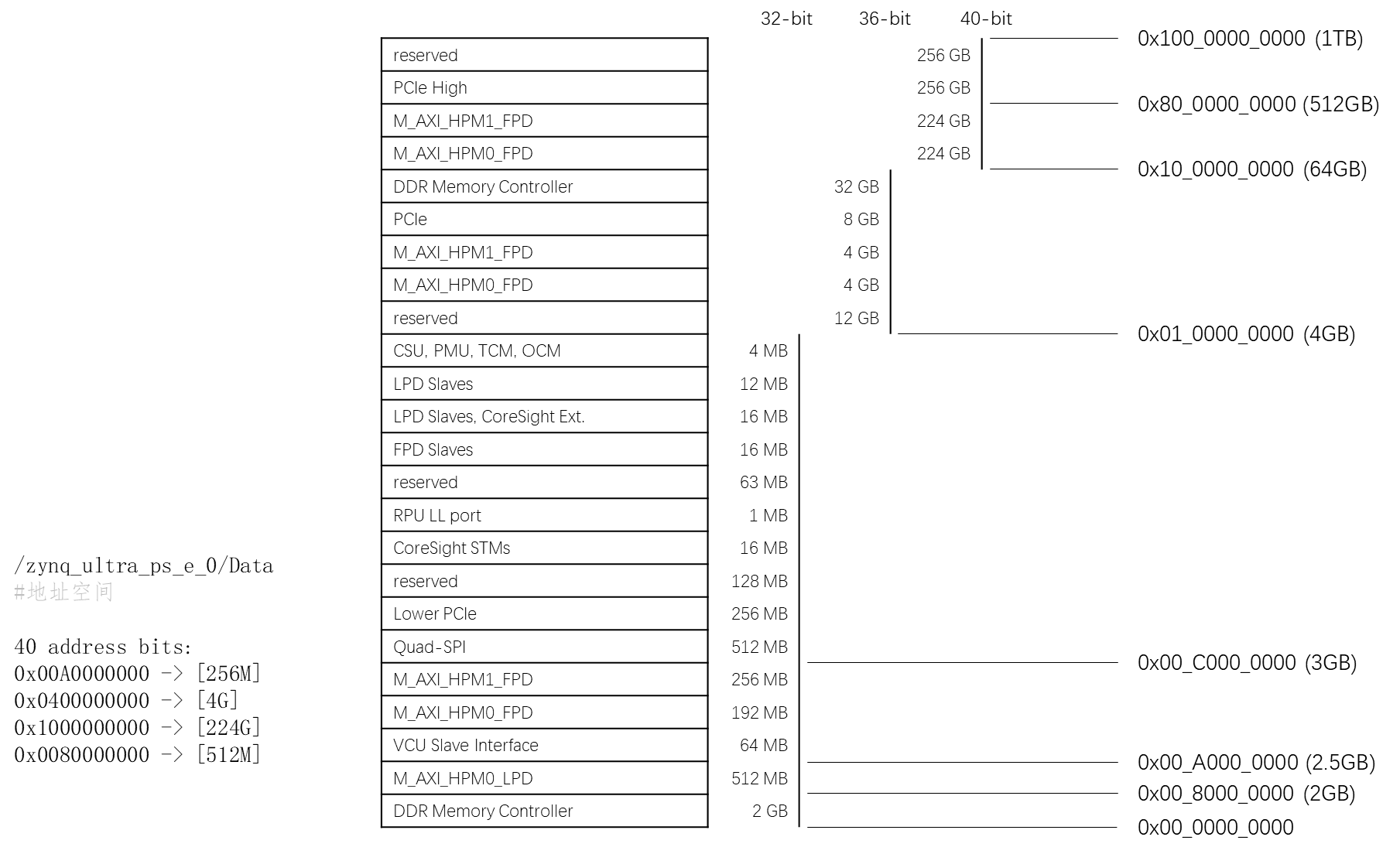

3.3 地址空间

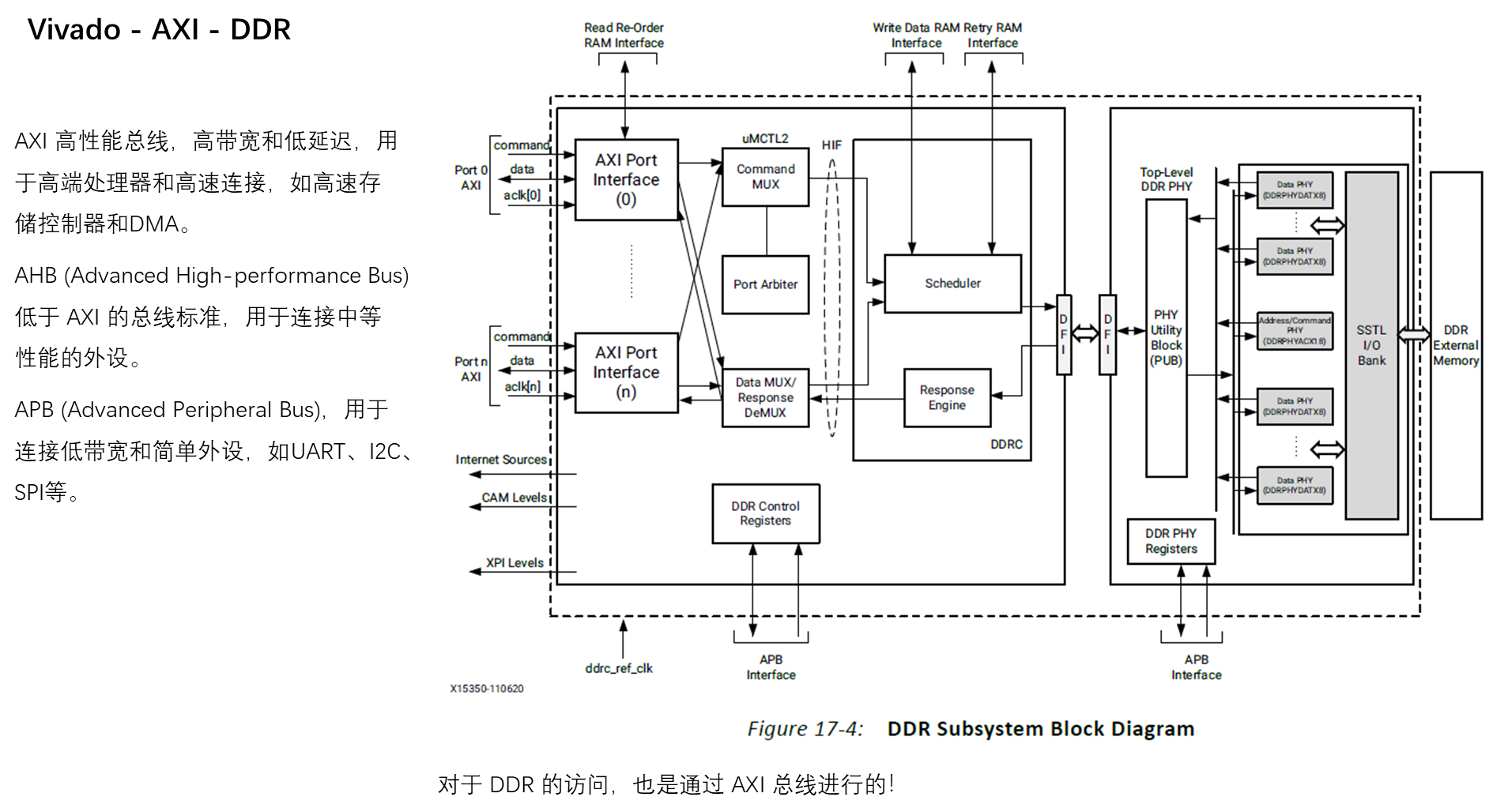

3.4 AXI-DDR

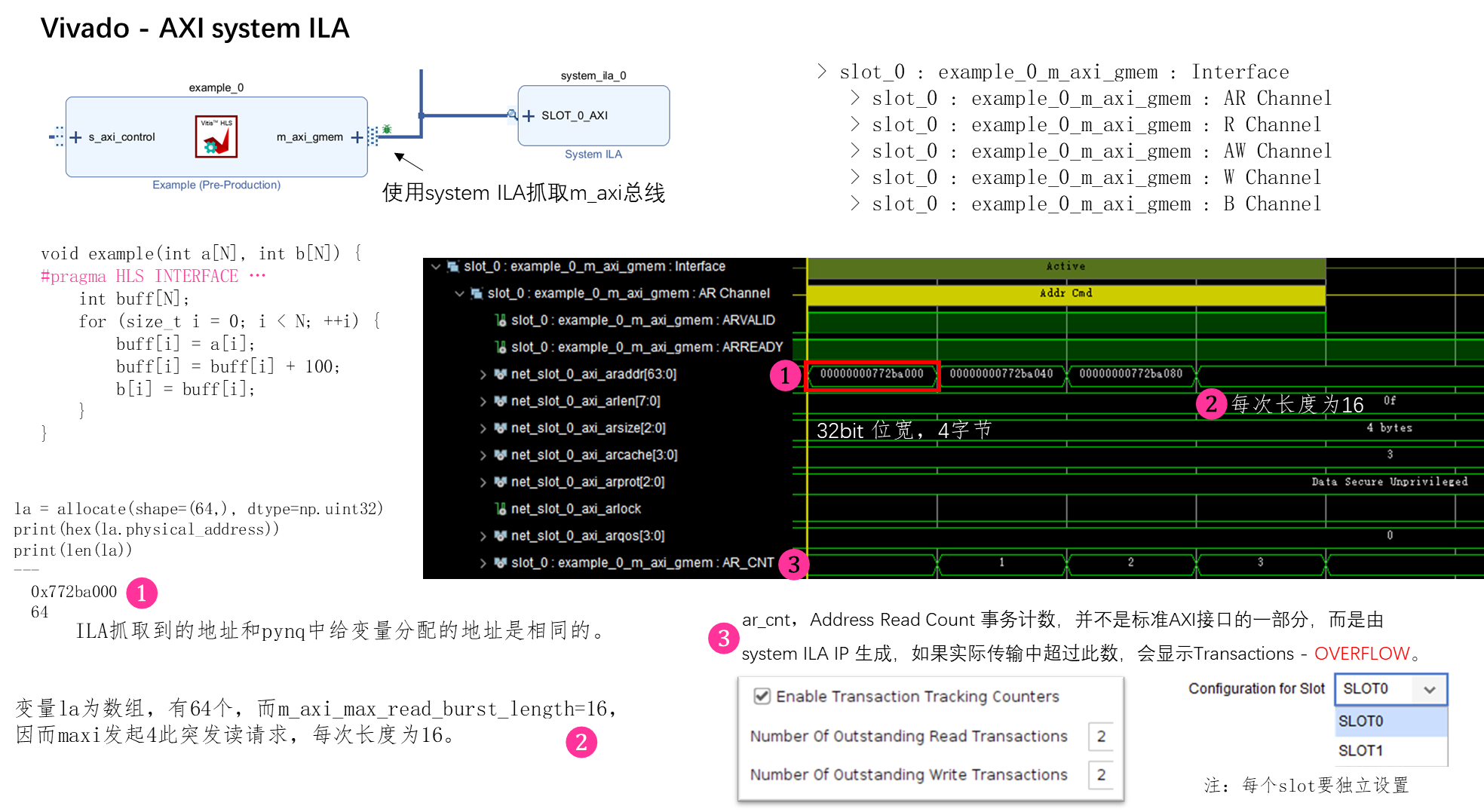

4. 通过ILA观察AXI信号

引入事务分析,可以清晰看到每次突发传输的起止范围

4.1 AXI 读通道

4.2 AXI 写通道