- 物理接口: SCL + SDA

(1)SCL(serial clock):时钟线,传输CLK信号,一般是I2C主设备向从设备提供时钟的通道。

(2)SDA(serial data):数据线,通信数据都通过SDA线传输

. 通信特征:串行、同步、非差分、低速率

(1)I2C属于串行通信,所有的数据以位为单位在SDA线上串行传输。

(2)同步通信就是通信双方工作在同一个时钟下,一般 通信的A方通过一根CLK信号线传输A自己的时钟给B,B工作在A传输的时钟下。所以同步通信的显著特征就是:通信线中有CLK。

(3)非差分。因为I2C通信速率不高,而且通信双方距离很近,对干扰不敏感,所以使用电平信号通信。

(4)低速率。I2C一般是用在同一个板子上的2个IC之间的通信,而且用来传输的数据量不大,所以本身通信速率很低(一般几百KHz,不同的I2C芯片的通信速率可能不同,具体在编程的时候要看自己所使用的设备允许的I2C通信最高速率,不能超过这个速率)

- 突出特征1:主设备+从设备

(1)I2C通信的时候,通信双方地位是不对等的,而是分主设备和从设备。通信由主设备发起,由主设备主导,从设备只是按照I2C协议被动的接受主设备的通信,并及时响应。

(2)谁是主设备、谁是从设备是由通信双方来定的(I2C协议并无规定),一般来说一个芯片可以只能做主设备、也可以只能做从设备、也可以既能当主设备又能当从设备。(像一些传感器芯片设计的时候只能做从设备,有的芯片本身既可以当主设备又可以当从设备,通过软件来配置是主设备还是从设备)

- 突出特征2:

(1)I2C通信可以一对一(一个主设备对1个从设备),也可以一对多(一个主设备对多个从设备)

(2)主设备负责调度总线,决定某一时间和哪个从设备通信。注意:同一时间内,I2C的总线上只能传输一对设备的通信信息,所以同一时间只能有一个从设备和主设备通信,其他从设备处于“冬眠”。不能出来捣乱,否则通信就乱套了。

(3)每一个I2C从设备在通信中都有一个I2C从设备地址,这个设备地址是从设备本身固有的属性,然后通信时主设备需要知道自己将要通信的那个从设备的地址,然后在通信中通过地址来甄别是不是自己要找的那个从设备。

- I2C的通信时序

(1)什么是时序?

字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

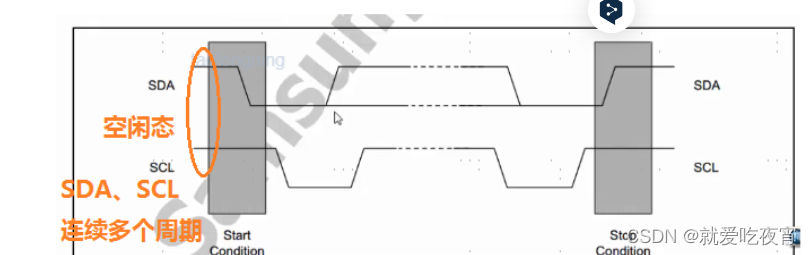

(2)I2C的总线空心状态、起始位、结束位

总线的意思就是SCL与SDA加起来就叫做总线。

I2C总线上有1个主设备,n(n>=1)个从设备。I2C总线上有2种状态:空闲态(所有从设备都未和主设备通信,此时总线空闲)和忙态(其中一个从设备在和主设备通信,此时总线被这一对占用,其他从设备必须歇着)。

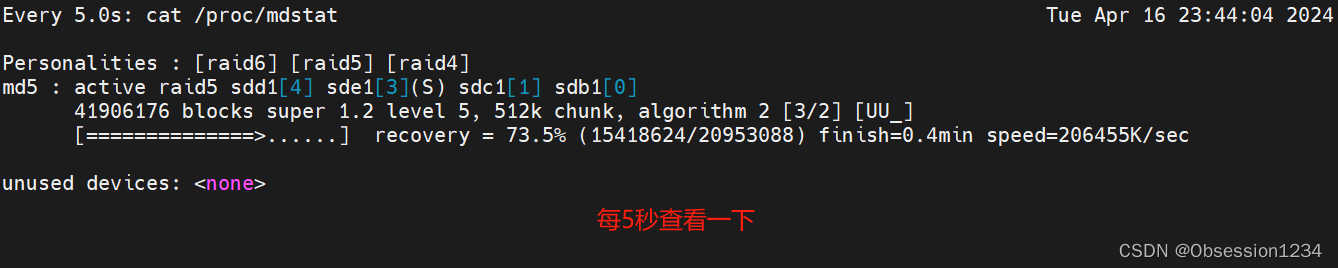

怎么区分总线处于空闲态,SDA、SCL在通信的过程中也可能同时为高电平,但是,如果SDA、SCL如果连续多个周期同时处于高电平,则总线一定处于空闲态。

整个通信分为一个周期一个周期的,两个相邻的通信周期是空闲态。每一个通信周期由一个起始位开始,一个结束位结束,中间是本周期的通信数据。

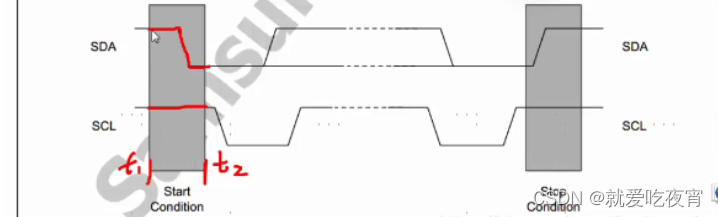

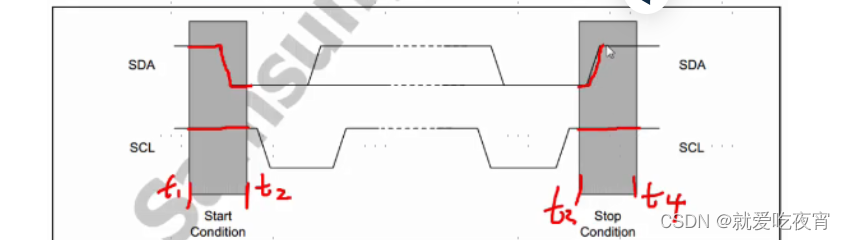

起始位:起始位说的不是一个时间点,而是一个时间段,如上图的t1到t2这个时间段,在t1到t2的这个时间段内,SCL一直保持了高电平,SDA由高电平到低电平跳变(下降沿)。接收方在接收到这样一个电平变化之后就知道发送方要开始发送数据了,紧接着下一个周期就是数据,

停止位:与起始位相似,结束位也是一个时间段。在这段时间内总线状态变化情况是:SCL先维持高电平,同时SDA线发生一个从低电平到高的上升沿。

起始位和停止位中间的就是通信位。CLK上升沿锁存数据,CLK上升沿到来前SDA要提前准备好数据。

A是应答信号,从设备的应答是为了让主设备知道自己已经接收到了主设备的信息。相应的主设备的应答也是如此。

- I2C数据传输格式(数据位&ACK)

(1)每一个通信周期的发起和结束都是由主设备来做的,从设备只有被动的响应主设备,没法自己自发的去做任何事情。

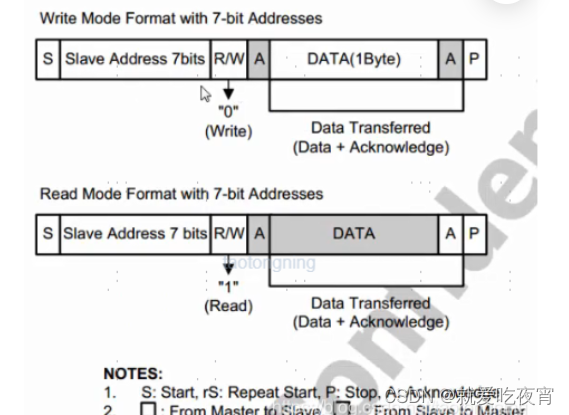

(2)主设备在通信周期会先发8位的从设备地址(其实8位中只有7位是从设备地址,还有1位表示主设备下面要写入还是读出)到总线(主设备是以广播的形式发送的,只要是总线上的所有从设备其实都能收到这个信息)。然后总线上的每个从设备都能收到这个地址,并且收到地址后和自己的设备地址比较看是否相等。如果相等说明主设备本次通信 就和给我说话,如果不相等说明这次通信与我无关,不用听了不管了。

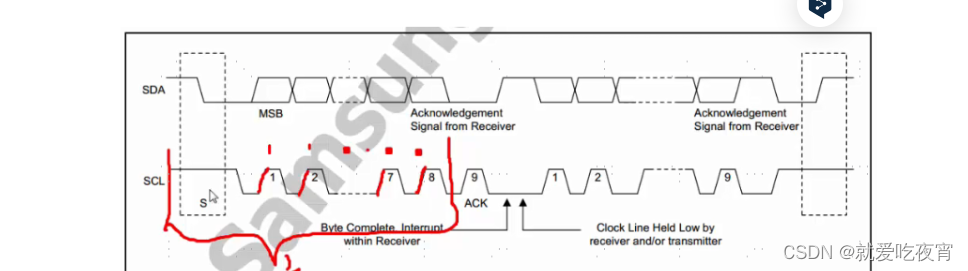

(3)发送方发送一段数据后,接收方需要回应一个ACK。这个响应本身只有1个bit位,不能携带有效信息,只能表示2个意思(要么表示收到数据,即有效响应;要么表示未收到数据,无效响应),需要注意的是,到第九个周期的时候,主设备会释放SDA,即让其变为高电平,从设备会主动来拉低SDA,主设备会读取此时的SDA,若读取此时的SDA为则表示从设备已经收到刚刚发送的信息,若读取此时的SDA为则表示从设备没有收到刚刚发送的信息。

(4)在某一个通信时刻,主设备和从设备只能有一个在发(占用总线,也就是向总线写),另一个在收(从总线读)。如果在某个时间主设备和从设备都试图向总线写那就完蛋了,通信就乱套了。

- 数据在总线上的传输协议

(1)I2C通信时的基本数据单位也是以字节为单位的,每次传输的有效数据都是1个字节(8位)。

(2)起始位及其后的8个clk中都是主设备在发送(主设备掌控总线),此时从设备只能读取总线,通过读总线来得知主设备发给从设备的信息;然后到了第9个周期,按照协议规定从设备需要发送ACK给主设备,所以此时主设备必须释放总线(主设备把总线置为高电平然后不要动,其实就类似于总线空闲状态),同时从设备试图拉低总线发出ACK。如果从设备拉低总线失败,或者从设备根本就没有拉低总线,则主设备看到的现象就是总线在第9周期仍然一直保持高,这对主设备来说,意味着我没有收到ACK,主设备就认为刚才给从设备发送的8字节不对(接收失败)。

(3)由于I2C的速率很低,完全可以通gpio来模拟。

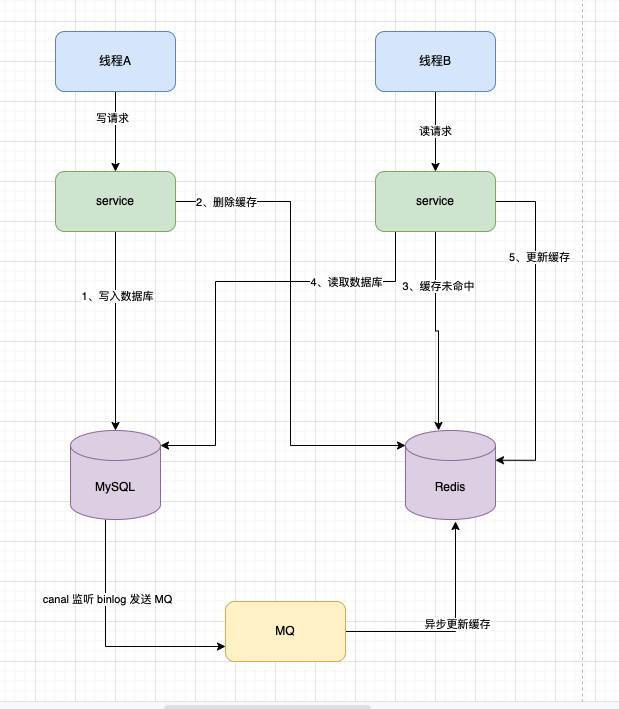

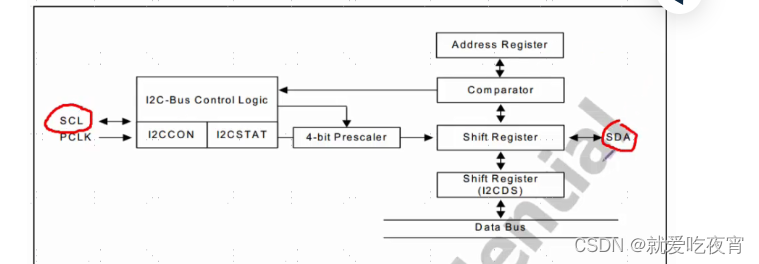

8. I2C控制器

通信双方本质上是通过时序在工作,但是时序会比较复杂不利于Soc软件完成,于是乎解决方案是soc内部内置了硬件的控制器来产生通信时序。这样我们写软件时只需要向控制器的寄存器中写入配置值即可,控制器会产生适当的时序在通信线上和对方通信。

(1)时钟部分,时钟来源是PCLK_PSYS,经过内部分频最终得到I2C控制器的CLK,通信中这个CLK会通过SCL线传给从设备。

(2)I2C总线控制逻辑(前台代表是I2CCON、I2CSTAT这两个寄存器),主要负责产生I2C通信时序。实际编程中要发送起始位、停止位、接收ACK等都是通过这两个寄存器(背后所代表的电路模块)实现的。

(3)移位寄存器(shift register),将代码中要发送的字节数据,通过移位寄存器变成1个位一个位的丢给SDA线上去发送/接收。

(4)地址寄存器+比较器 本I2C控制器做从设备的时候用。