Zynq 是 Xilinx 公司提出的全可编程 SoC 架构,集成了单核或多核 ARM 处理器与 Xilinx 16nm 或 28nm 可编程逻辑,包括 Zynq 7000 Soc,Zynq UltraScale+ MPSoC 和 Zync UltraScale+ RFSoC 等系列。本文主要介绍 Xilinx Zynq 7000 系列芯片架构、功能与开发流程。

目录

1. ZYNQ 概述

1.1 ZYNQ 的架构与组成

1.2 ZYNQ 的功能与特性

1.2.1 APU

1.2.2 存储器接口

1.2.3 I/O 外设

1.2.4 互联块

1.2.5 CLBs, Slices, and LUTs

1.2.6 时钟管理单元

1.2.7 Block RAM, DSPs

1.2.8 Input/Output

2. ZYNQ 开发流程

1. ZYNQ 概述

Zynq 是 Xilinx 公司推出的可编程 SoC 架构,集成了单核或多核 ARM 处理器与 Xilinx 16nm 或 28nm 可编程逻辑,包括 Zynq 7000 Soc,Zynq UltraScale+ MPSoC 和 Zync UltraScale+ RFSoC 等系列。

Zynq 7000 SoC 系列

- 单核或双核 ARM Cortex-A9 处理器

- 28nm Artix 7 或 Kintex 7 可编程逻辑

- 支持 6.25Gb/s 至 12.5Gb/s 收发器

Zynq UltraScale+ MPSoC 系列

- 双核或四核 ARM Cortex-A53 处理器

- 双核 ARM Cortex-R5F 处理器

- 16nm FinFET+ 可编程逻辑

- H.264/H.265 视频编解码器

Zynq UltraScale+ RFSoC 系列

- 四核 ARM Cortex-A53 处理器

- 双核 ARM Cortex-R5F 处理器

- 16nm FinFET+ 可编程逻辑

- 数字 RF-ADC,RF-DAC,SD-FEC

ZYNQ 的优势:

- 单片集成处理器与可编程逻辑,降低硬件设计复杂性;

- 提供全可编程(软件、硬件)能力,用途灵活;

- 提供广泛的行业标准工具和 IP 库;

- 相比多芯片设计,更低功耗。

ZYNQ 中的嵌入式处理器可运行操作系统和应用程序,可编程逻辑部分可用于实现复杂、对实时性能要求高的信号处理。ZYNQ 具有 ARM 处理器的软件可编程性,以及 FPGA 的硬件可编程性,因此也被称为全可编程 SoC(All Programmable SoC,APSoC)。

ZYNQ 具有高度可配置和更加灵活的特点,可以应用于通信、汽车驾驶、消费电子等领域。

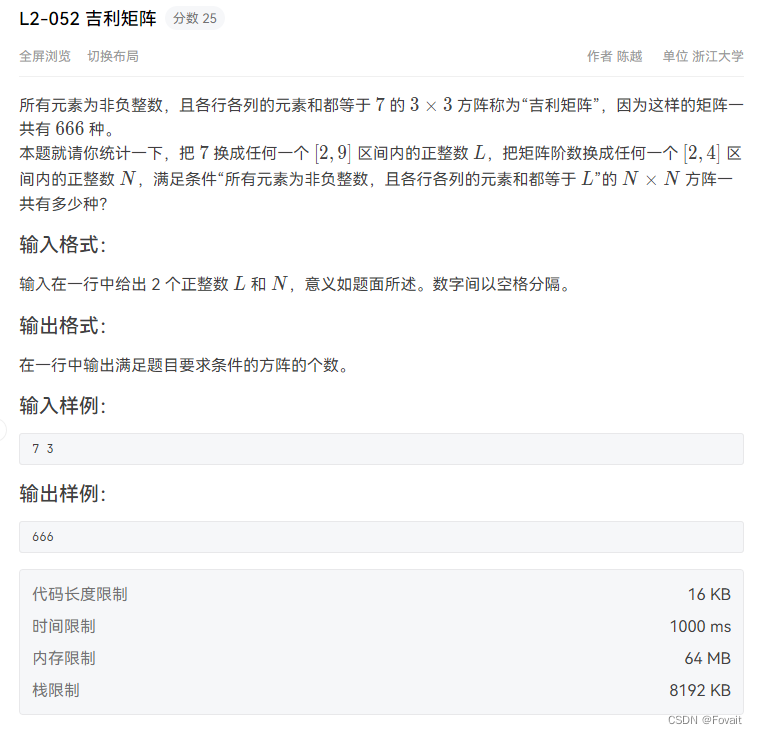

1.1 ZYNQ 的架构与组成

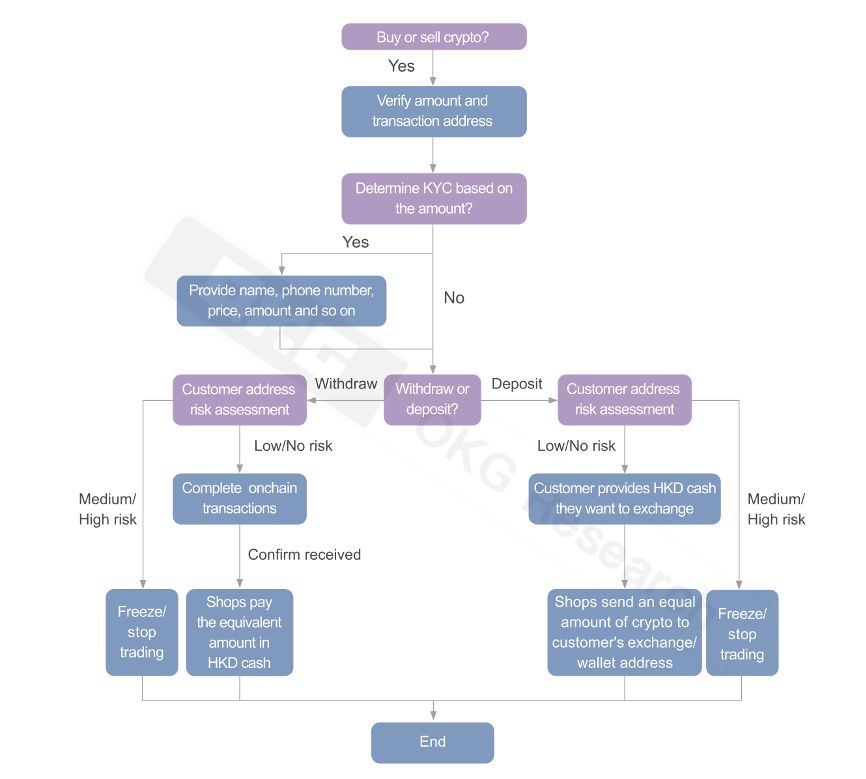

本节主要介绍 Xilinx Zynq-7000 系列芯片架构。Zynq-7000 SoC 主体架构相似,主要由嵌入式处理器(Process System)、可编程逻辑块(Programmable Logic),以及 PS 与 PL 之间的互连线组成。

嵌入式处理器部分采用双核 ARM Cortex-A9 处理器,每个处理器核心都支持 Neon 指令集,单/双精度浮点运算,外设支持 2 x UART, 2 x CAN 2.0B, 2 x I2C, 2 x SPI 和 4 x 32位 GPIO,以及 2 x USB 2.0 (OTG), 2 x 三态千兆以太网, 2 x SD/SDIO。

Zynq-7000 SoC 器件包含 Z-7010、Z-7015、Z-7020、Z-7030、Z-7035、Z-7045 和 Z-7100 型号,不同型号包含的可编程逻辑资源见下表。

Zynq 嵌入式处理器 PS 与可编程逻辑 PL 之间还有以下接口:

- 2 x 32bit 主 AXI 接口

- 2 x 32bit 从 AXI 接口

- 4 x 64-bit/32-bit AXI 存储接口

- 64 位 ACP

- 16 个中断

1.2 ZYNQ 的功能与特性

PS 的四个主要部分:

1)应用处理单元(APU)

2)存储器接口

3)I/O 外设

4)互联块

PL 的四个主要部分:

1)CLBs, Slices, and LUTs

2)时钟管理单元

3)Block RAM, DSPs

4)Input/Output

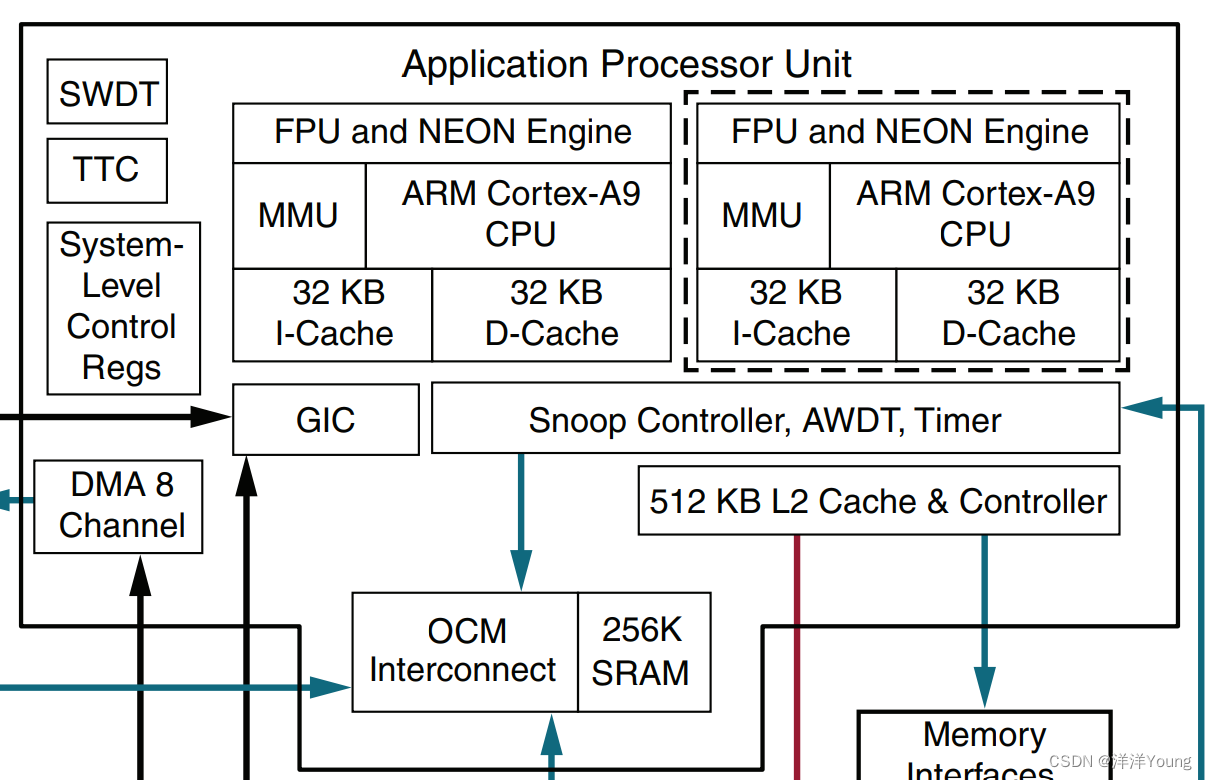

1.2.1 APU

APU 部分主要特点如下:

- 双核 ARM Cortex-A9 处理器

- 处理能力 2.5 DMIPS/MHz

- 工作频率:667MHz ~ 1GHz

- 单精度,双精度浮点运算能力:2.0 MFLOPS/MHz

- 支持 SIMD 的 NEON 媒体处理引擎

- Level 1 caches,指令与数据各 32KB

- 集成内存管理单元(MMU)

- Level 2 Cache(512KB)

- 双端口片上 RAM(256KB)

- 8 通道 DMA

- 支持多种传输类型:memory-to-memory, memory-to-peripheral, peripheral-to-memory, and scatter-gather

- 64 位 AXI 接口,支持高吞吐量 DMA 传输

- 4 个通道 PL 端专用

- 中断与定时器

- 通用中断控制器(GIC)

- 3 x 看门狗定时器

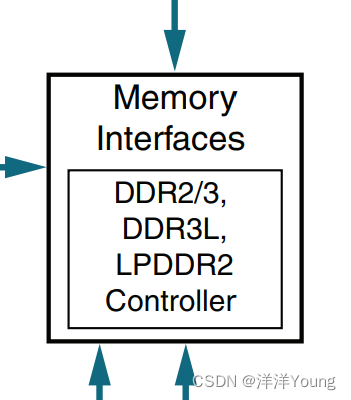

1.2.2 存储器接口

Zynq 存储器接口单元包括动态存储器控制器和静态存储器接口模块。动态内存控制器支持 DDR3、DDR3L、DDR2 和 LPDDR2 内存。静态内存控制器支持 NAND 闪存接口、Quad-SPI 闪存接口、并行数据总线和并行 NOR FLASH 接口。

- 动态存储器接口

- DDR 控制器提供对 1Gb 地址的访问,可配置为 16-bit 或 32-bit 位宽

- DDR3 支持速率高达 1333Mb/s

- PS 与 PL 可共享 common 存储的访问

- 支持 4 个 AXI 接口:1 个 ARM CPU 专用(通过 L2 Cache 控制器)、2 个 PL 端专用、1 个通过 central interconnect 与主 AXI 接口共享

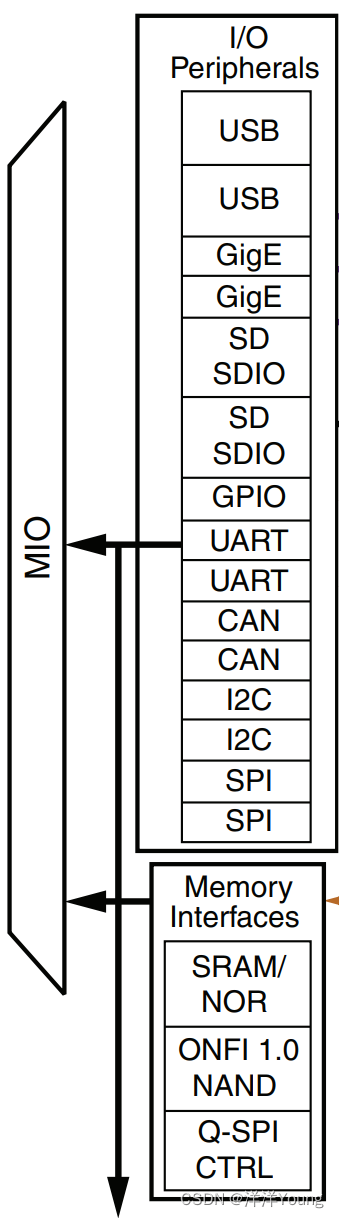

- 静态存储器接口

- 8-bit SRAM 数据总线

- 8-bit 并行 NOR FLASH 接口

- ONFi 1.0 NAND flash,支持 1-bit ECC

- 1-bit SPI, 2-bit SPI, 4-bit SPI (quad-SPI), or two quad-SPI (8-bit) 串行 NOR flash

1.2.3 I/O 外设

I/O 外设主要用于数据传输,主要特点如下:

- 2 个 10/100/1000M 以太网 MAC 接口

- 支持 IEEE Std 802.3 与 IEEE Std 1588 revision 2.0 标准

- Scatter-gather DMA 功能

- 支持外部 PHY 接口

- 2 个 USB 2.0 OTG 外设,每个外设支持多达 12 个端点

- 支持高速、全速模式

- 支持 Host、Device 与 Ob-The-Go 配置

- 使用 32 位 AHB DMA 主接口和 AHB 从接口

- 提供 8 位 ULPI 外部 PHY 接口

- 符合英特尔 EHCI 标准的 USB 主机控制器寄存器和数据结构

- 2 个 CAN 总线接口控制器

- 符合 CAN 2.0B 标准

- ISO 118981-1

- 2 个 SD/SDIO 控制器

- 符合 SD/SDIO 2.0 标准

- 2 个 全双工 SPI 端口

- 2 个 UART 接口

- 2 个 IIC 接口

- 118-bit GPIO

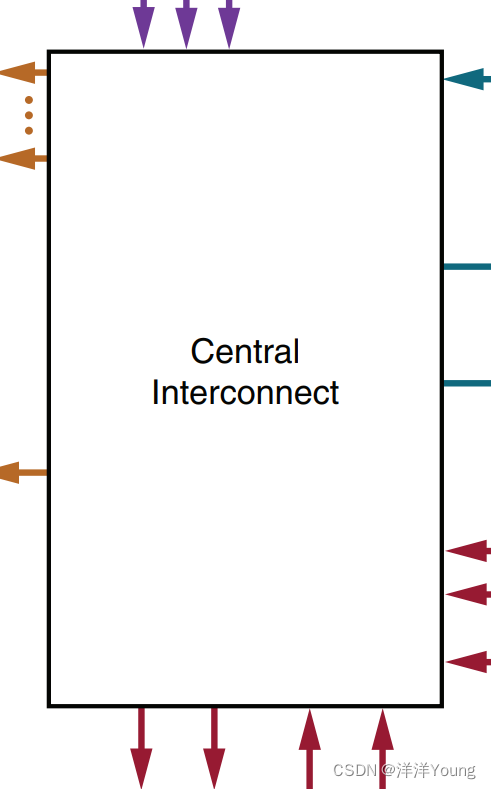

1.2.4 互联块

APU、内存接口单元和 IOP 都通过多层 AMBA AXI 总线互连,包括到 PL 端。互连是非阻塞的,支持多个同时进行的主从传输。

通过互连的流量可以通过互连中的 Quality of Service (QoS) 块进行调节。QoS 主要用于调节 CPU、DMA 控制器和表示 IOP 中主节点的组合实体生成的流量。

1.2.5 CLBs, Slices, and LUTs

Zynq 可编程逻辑块(CLBs)主要特性如下:

- 6 输入 LUT 结构

- 每个 CLB 包含 2 个 Slice,每个 Slice 包含 4 个 LUTs,8 个 Flip-Flops

- 可作为单个 64-bit ROM,或者 2 个具有共用地址的 32bit ROM

- 25-50% 的 Slice 可作为分布式 64-bit RAM,或者 32-bit/16-bit 移位寄存器

1.2.6 时钟管理单元

Zynq-7000 系列中的每个器件都具有多达 8 个时钟管理模块 (CMT),每个模块由一个混合模式时钟组成管理器 (MMCM) 和一个锁相环 (PLL)。

Zynq 时钟管理单元主要特性如下:

- 高速缓冲器与布线,用于低偏斜的时钟分布

- 频率综合与相位调节

- low-jitter 时钟生成

Zynq-7000 系列提供六种不同类型的时钟缓冲器(BUFG、BUFR、BUFIO、BUFH、BUFMR 和高性能时钟),以满足高扇出、短传播延迟和极低偏移等不同时钟要求。

1.2.7 Block RAM, DSPs

Zynq-7000 系列具有多达 755 个双端口块 RAM,每个 RAM 可存储 36 Kb。每个块 RAM 有两个完全独立的端口,共享存储的数据。

Block RAM 的主要特性如下:

- 双端口 36 Kb 块 RAM,端口宽度高达 72-bit

- 可编程 FIFO 逻辑

- 内置可选纠错电路

Block RAM 每个端口可以配置为 32K × 1、16K × 2、8K × 4、4K × 9(或 8)、2K × 18(或 16)、1K × 36(或 32)或 512 × 72(或 64)。每个块 RAM 可以分为两个完全独立的 18 Kb 块RAM。

Zynq-7000 系列器件每个 DSP Slice 基本上由一个专用的 25×18 位二进制补码乘法器和一个48 位累加器组成,工作频率均高达 741 MHz。DSP 包括一个额外的预加法器,通常用于对称滤波器,可提高密集封装设计中的性能。

1.2.8 Input/Output

Zynq-7000 系列器件的 I/O 数量,随着器件型号和封装类型的不同而变化。每个 I/O 都是可编程的,支持多种 I/O 标准。Zynq-7000 I/O 资源分为 2 种,High Range(HR)与 High Performance(HP)。HR I/O 提供宽电压范围,支持 1.2V ~ 3.3V 电平标准,而 HP I/O 用于高性能工作场景,支持 1.2V ~ 1.8V 电平标准。

2. ZYNQ 开发流程

未完待续 ~

![[阅读笔记20][BTX]Branch-Train-MiX: Mixing Expert LLMs into a Mixture-of-Experts LLM](https://img-blog.csdnimg.cn/direct/8751e7253f134d69b3387fceb546fff5.png)