咸鱼25计组强化课P2的笔记,有点简陋。

课后需要把第三章的课后大题(真题做一下)

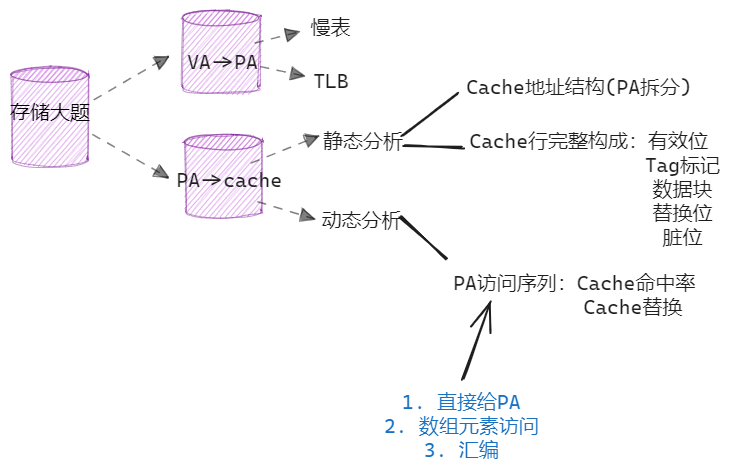

Cache类题目

做题要注意的点!!

- PA的位数=Cache地址总位数

- Cache总行数

- Cache块大小

- 第2和第3相乘得Cache数据区总大小(!=Cache总大小)

- 映射方式

- 一致性问题:写策略(直写/回写)

- 替换算法

- CPU先把VA翻译成PA,再用PA去访问Cache

求地址结构

先根据映射方式确定行号/组号和块内地址的位数,剩下的是Tag

映射方式

-

直接映射

Cache地址拆分为 Tag+行号+块内地址。

直接映射相当于1行1组

行号位数与总行数关系:$n = log_2{lines}$ -

组相联映射

Cache地址拆分为 Tag+组号+块内地址。

n路组相联,1组有n行

组数为总行数除以路数:$z=\frac{lines}{n}$ -

全相联映射

Cache地址拆分为 Tag+块内地址。

只有1组

一致性问题

- 直写法:Cache中数据块只要修改过,就同步修改主存中的数据,因此不需要脏位。

- 回写法:Cache修改过的数据块先在1 bit 脏位标记,直到这个块即将被淘汰时写回主存。

替换算法

要替换时选择淘汰哪一个?

- 随机替换:不需要替换信息位,因为随机,不需要关心优先级和顺序。

- 直接映射也不需要替换位,因为1行1组,根据地址只能找到对应的1行/组

- 其他:n选1替换,需要$log_2 n$ 位

- FIFO:先进先出,替换位需要记录进入顺序。

- LRU:最近最少使用

- 组相联需要替换位 $log_2 n$ bits,n为路数

- 全相联需要替换位 $log_2 lines$ bits

例题

2020真题

(10分)假定主存地址为32位,按字节编址,指令Cache和数据Cache与主存之间均采用8路组相联映射方式,直写(Write Through)写策略和LRU替换算法,主存块大小为64B,数据区容量各为32KB。开始时Cache均为空。请回答下列问题。

(1)Cache每一行中标记(Tag)、LRU位各占几位?是否有修改位?

(2)有如下C语言程序段:

for(k = 0; k <1024; ++k)s[k] = * s[k];

若数组s及其变量k均为int型,int型数据占4B,变量k分配在寄存器中,数组s在主存中的起始地址为008000C0H,则该程序段执行过程中,访问数组s的数据Cache缺失次数为多少?

(3)若CPU最先开始的坊问操作是读取主存单元0001003H中的指令,简要说明从Cache中访问该指令的过程,包括Cache缺失处理过程。

分析(非答案):

(1).

抓重点

- 主存地址32位->PA 32位

- 8路组相联

- 直写

- LRU

- 主存块大小64B->块内地址占 6 bits

- 数据区32KB->行数=32KB/64B->组号=行数/路数

Tag(20 bits) + 组号(6 bits) + 块内地址(6 bits) = 32 bits

(2).

s[0] - 008000C0H

s[1] - 008000C4H

s[2] - 008000C8H

.......

同一Cache块内的不同元素,只有最后6 bits不一样

访问这些元素只有第一次会Cache缺失

这些元素总共填64块Cache块,会发生64此确实

(3).

根据地址找Cache

判断有效位->缺失

把64B的块读到Cache中

更新有效位、LRU替换位、Tag标记位

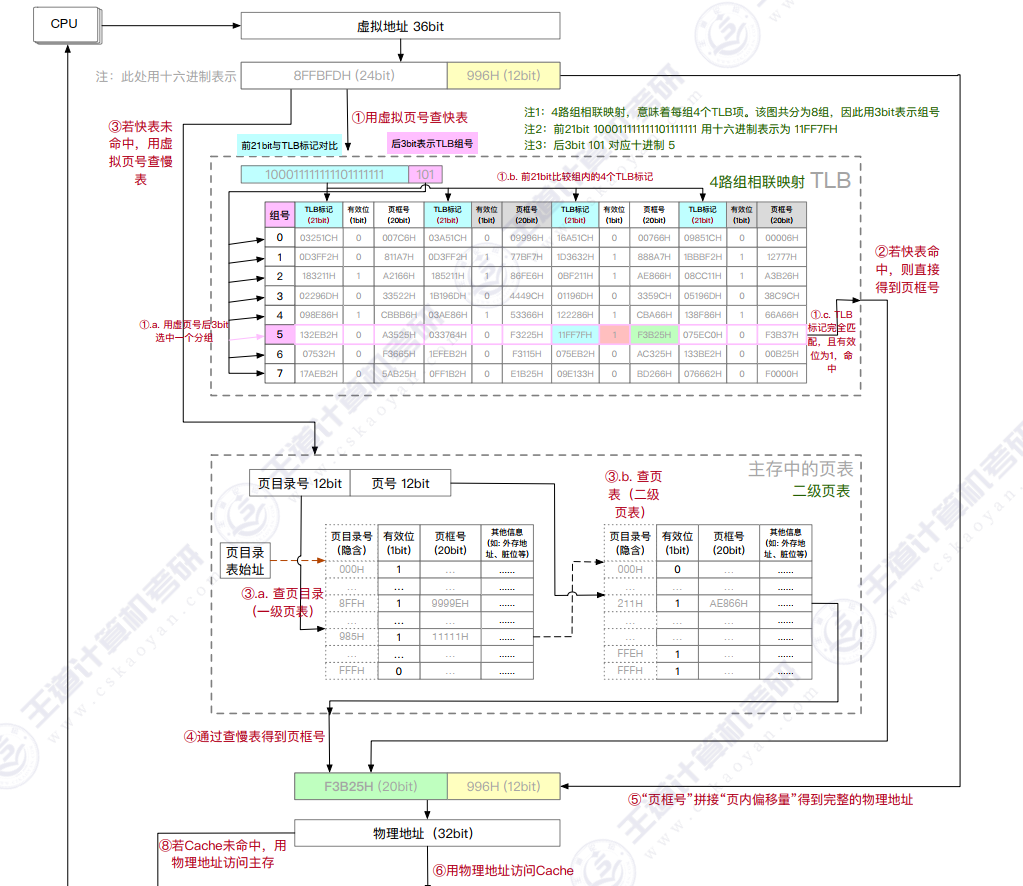

TLB类题目

用于VA->PA过程中,加快查询速度。原理与Cache类似

VA结构:页号+页内地址

做题要注意的点!!

- VA多少位,虚页号多少位,页内地址多少位(根据页大小确定)

- 映射方式:

- 一般没有直接映射,因为会发生TLB的抖动,导致频繁的换入换出,效率低下

- 组相联->K路:虚页号由Tag+组号构成,组号位数=$log_2 K$

- 全相联:虚页号=Tag,题目没说一般默认全相联

- 替换算法(同Cache)