- 简介

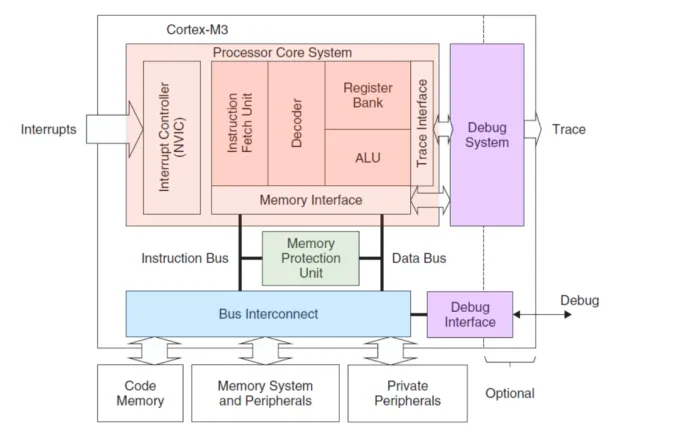

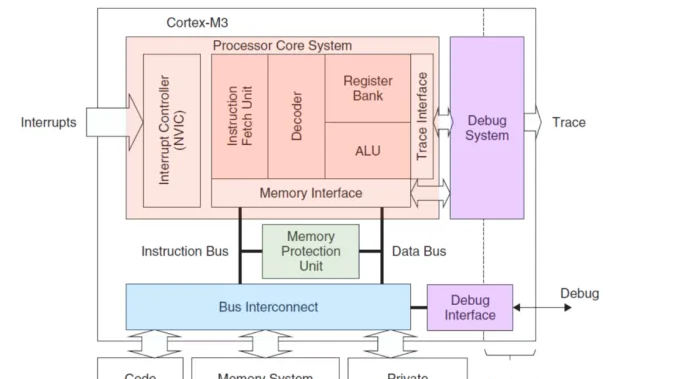

cortex-m3是一个32位处理器内核:总线(数据、地址)宽度是32位、寄存器位宽是32位;内核结构为哈佛结构,拥有独立的数据总线和指令总线,可以并行进行指令执行和数据访问;

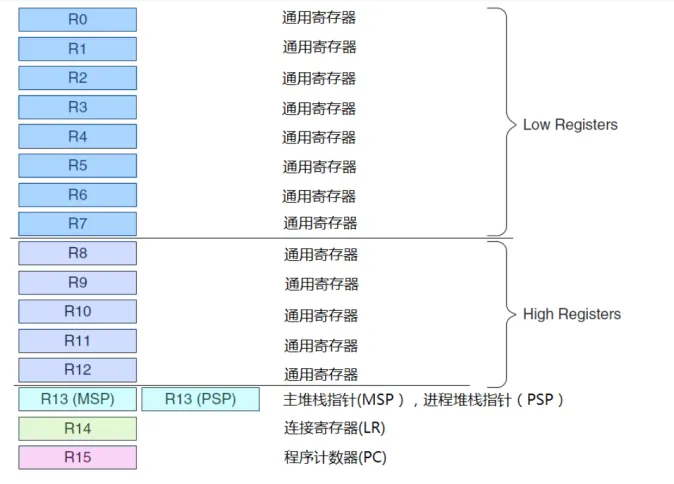

一、寄存器组

cortex-m3拥有R0-R15寄存器,其中R0-R12为通用寄存器

- 通用寄存器

通用寄存器用于数据操作,绝大多数16位thumb指令只能访问R0-R7,32位Thumb指令可以访问所有的

- Banked R13:MSP和PSP,两个堆栈寄存器,同一时刻只能使用其中一个,堆栈指针的低两位永远是0,堆栈总是4字节对齐的

- 主堆栈寄存器(MSP):复位后缺省使用的堆栈寄存器,用于操作系统内核和异常处理例程(包含中断服务程序

- 进程堆栈寄存器:由用户的应用代码使用

- R14连接寄存器LR

当调用一个函数时,LR记录调用函数返回的地址,当调用关系超过两层时,则会一级一级将函数的返回地址压入栈中

- R15程序计数寄存器PC

指向当前的程序运行地址

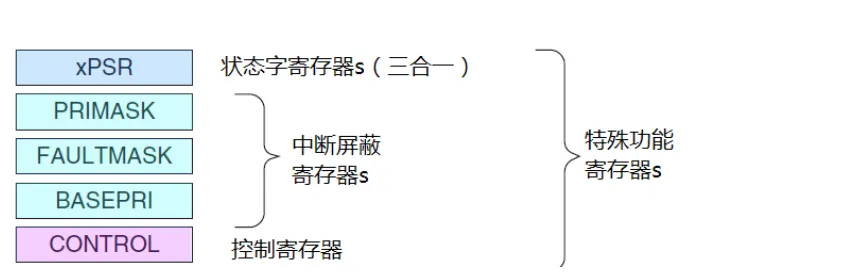

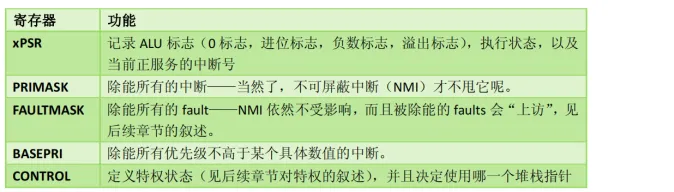

- 特殊功能寄存器

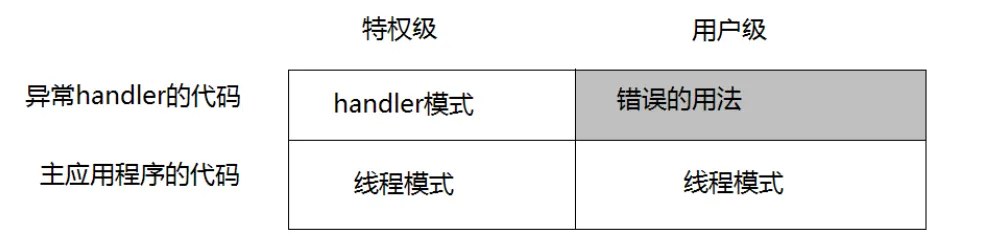

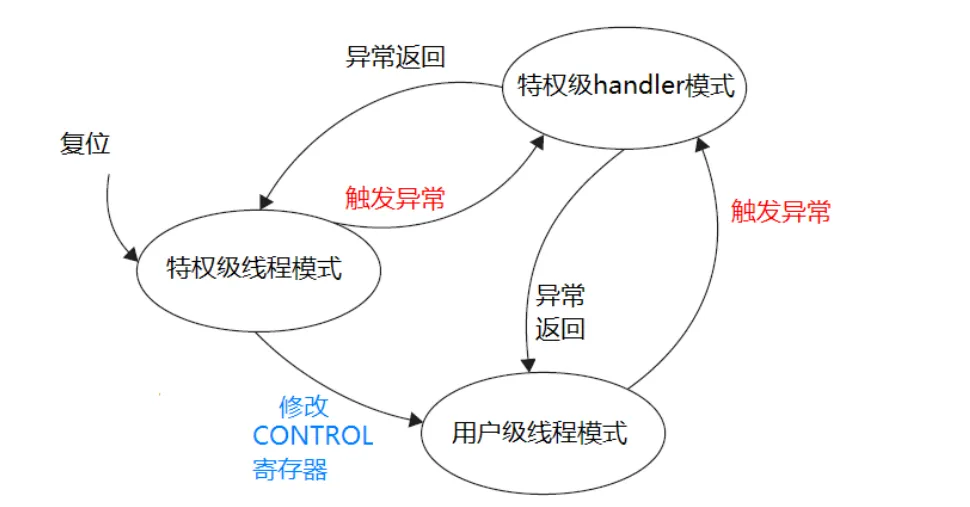

二、操作模式和特权级别

- 两种模式

- handler模式:当检测到中断、异常时运行的模式

- thread模式:用户应用程序运行

- 特权级别

- 特权级:处理器中比较高级的执行级别,可以执行任何指令、访问任何寄存器和存储器

- 用户级:访问受限的存储器空间和和系统资源,无法执行系统级别指令

三、内建的嵌套向量中断控制器(NVIC)

- 嵌套向量中断控制器负责管理微控制器的内部中断和外部中断请求,包含优先级管理、嵌套管理、使能禁用管理、挂起清除管理、向量表重定位管理。

- 嵌套向量中断控制器缩短中断延时、使控制器的中断更加的灵活好用

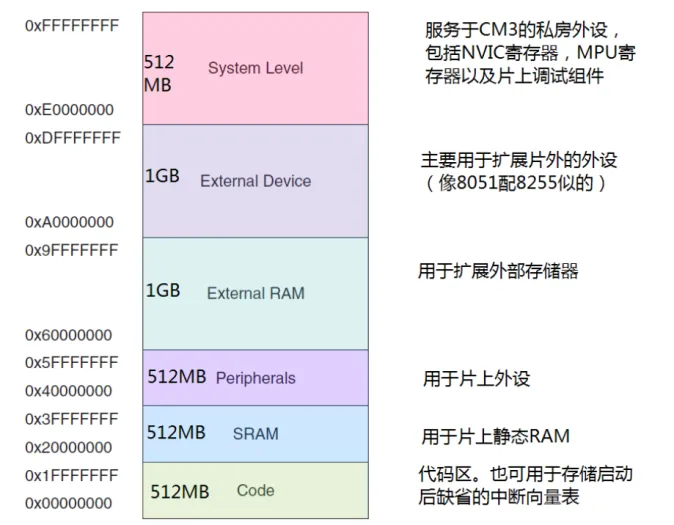

四、存储器映射

五、总线接口

cortex-m3内部拥有多个总线接口,可以同时进行取址和访问内存

- 指令存储总线(I-Code、D-Code):多code区的访问,负责代码运行时取指令和取数据

- 系统总线:CPU对内存和外设的访问、包含数据访问、地址访问和控制

- 外设总线:访问非共享的外设设备

六、存储器保护单元(MPU)

- 可以根据实际需求对不同的内存区域增加不同的访问权限,当检测到访问越限时mpu会产生一个fault异常。

- 可以利用MPU实现多进程系统,实现多个进程独享内存空间。

- 可以将固定区域设定权限,保证数据访问的安全性和隐私性

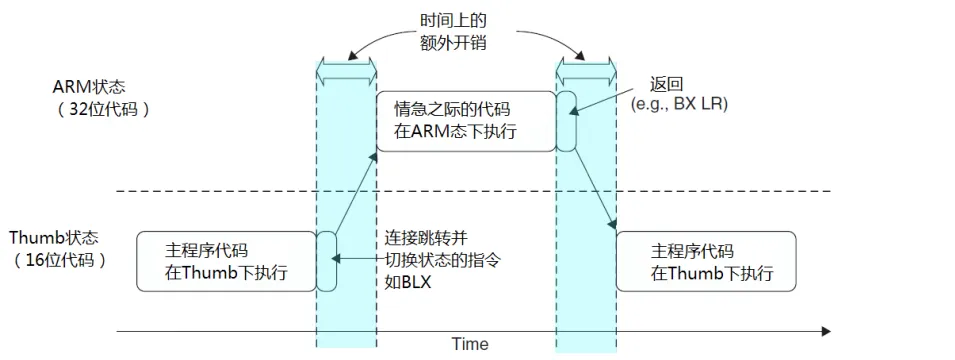

七、指令集

cortex-m3只使用thumb-2指令集,既允许32位指令又允许16位指令。

- 指令举例

- UBFX,BFI,BFC;位段提取、插入、清零,支持C位段,简化外设寄存器的操作

- CLZ,RBIT;计算前导指令和位反转指令

- UDIV,SDIV;无符号除法和带符号除法

- SEV,WFE,WFI;发送事件、等待事件和等待中断,可以用于多处理器之间的任务同步和休眠管理

- MSR,MRS;访问特殊功能寄存器

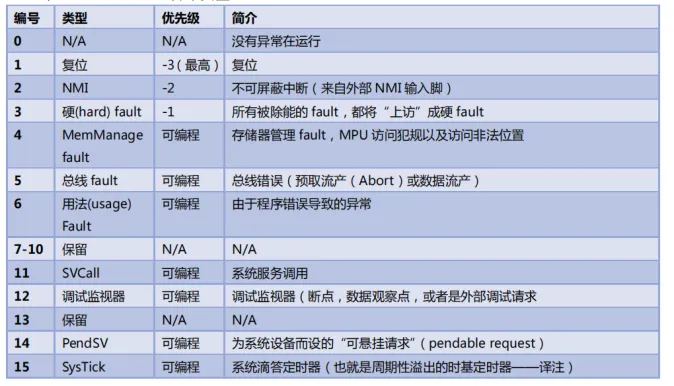

八、中断和异常

- CM3支持240条中断和11个内部异常,可以实现fault管理机制

- CM3去掉了FIQ机制,但是使用NVIC能实现更好的FIQ功能

- 支持NMI(不可屏蔽中断)输入引脚,当这个中断触发时,NMI服务例程会无条件执行

九、调试支持

- cortex-m3提供了程序执行控制、暂停、单步执行、指令断点、数据观察、寄存器存储器访问等各种调试跟踪机制

- 支持停机模式和监视器模式

- 支持JTAG和SW两种主机调试接口,通过DAP与调试器进行通信

- 支持调试信息输出,允许软件在运行时将控制台消息通过调试口输出

- 支持对时钟周期、指令执行数、中断开销进行计数统计,有助于对系统的性能分析和优化

cortex-m3是一个32位处理器内核:总线(数据、地址)宽度是32位、寄存器位宽是32位;内核结构为哈佛结构,拥有独立的数据总线和指令总线,可以并行进行指令执行和数据访问;

cortex-m3是一个32位处理器内核:总线(数据、地址)宽度是32位、寄存器位宽是32位;内核结构为哈佛结构,拥有独立的数据总线和指令总线,可以并行进行指令执行和数据访问;