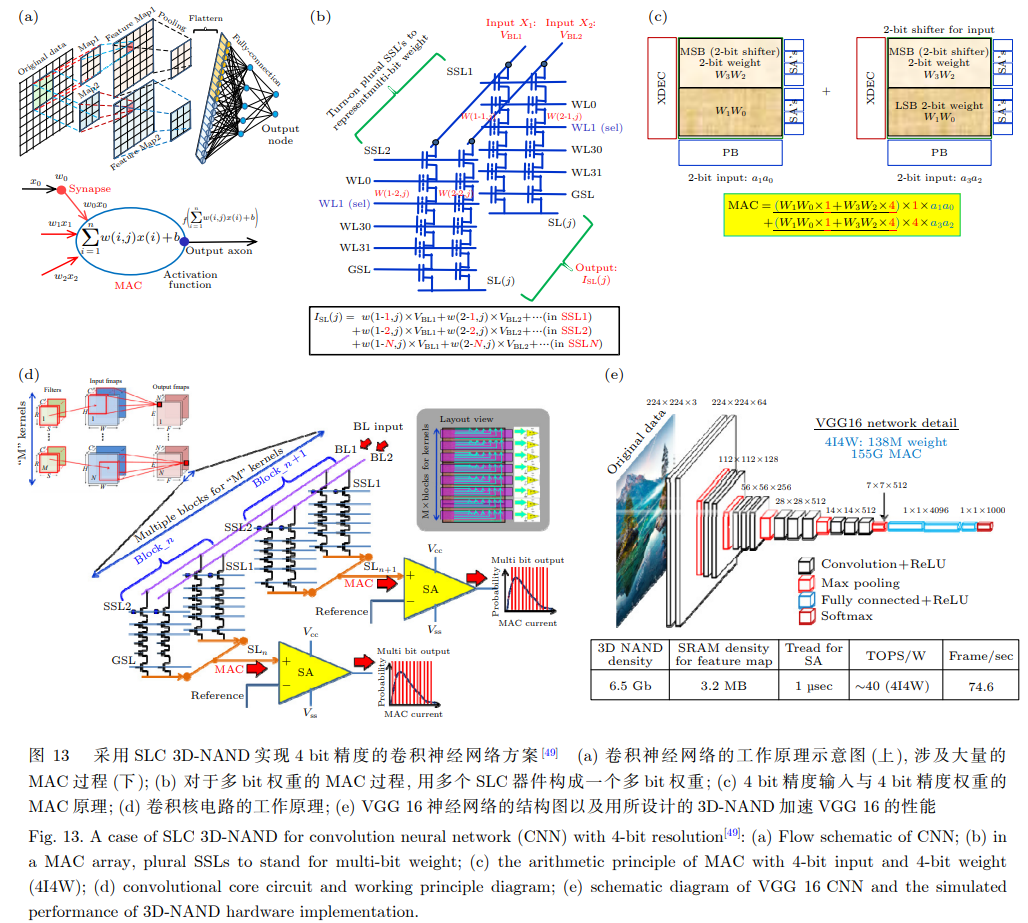

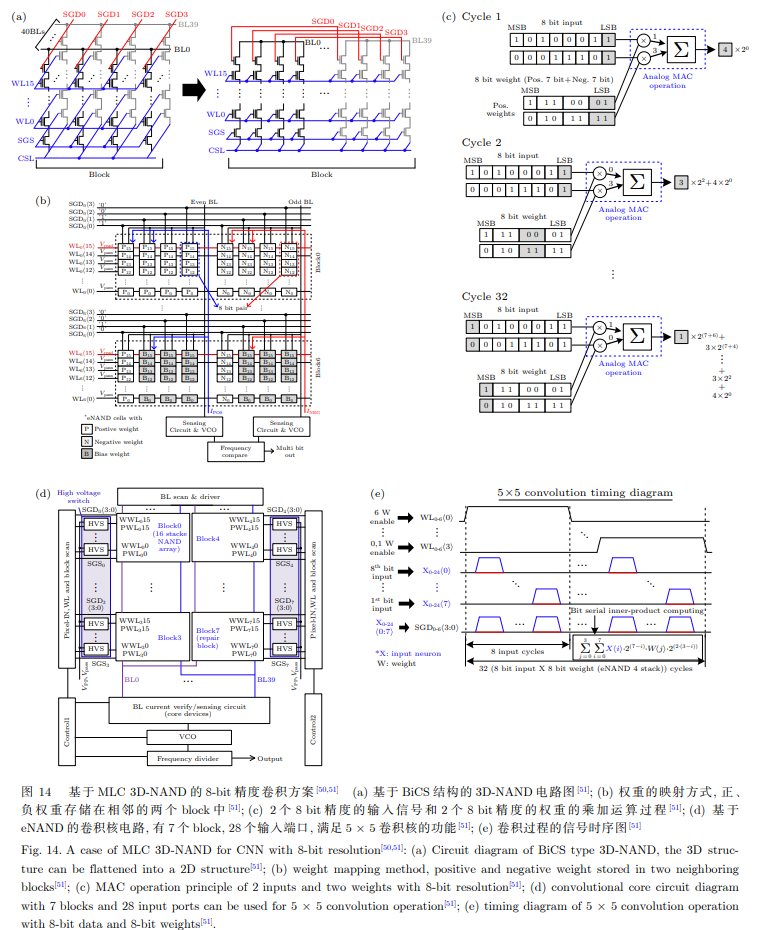

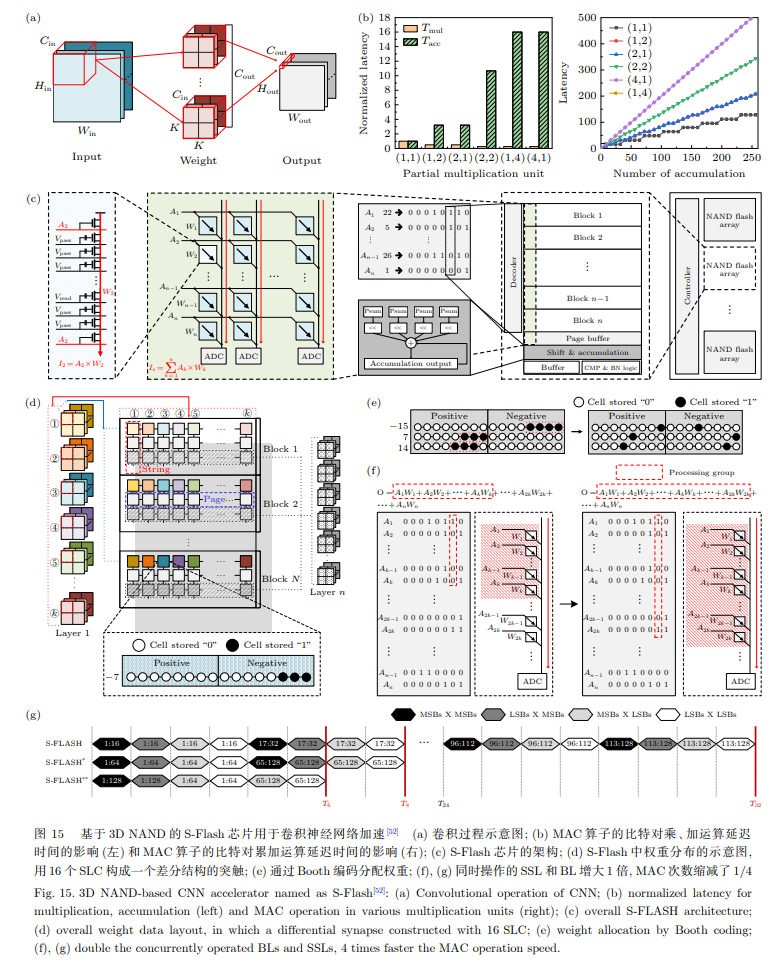

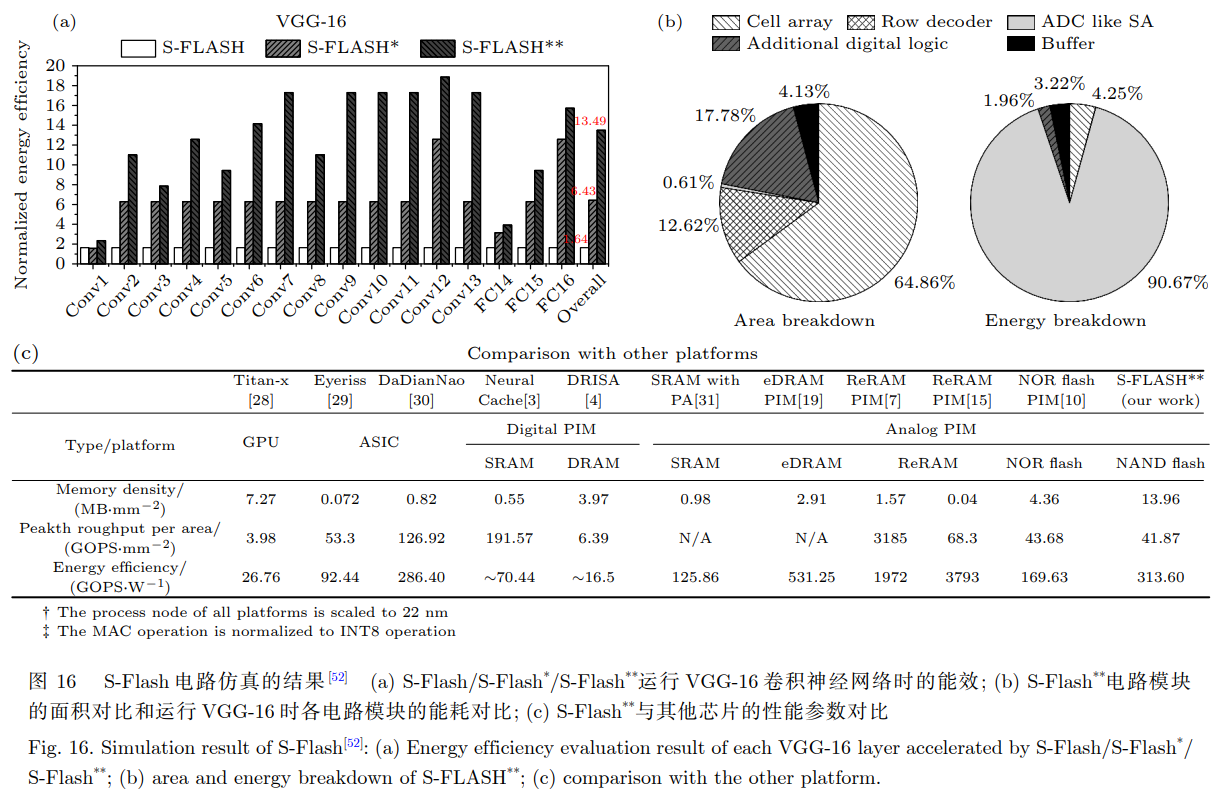

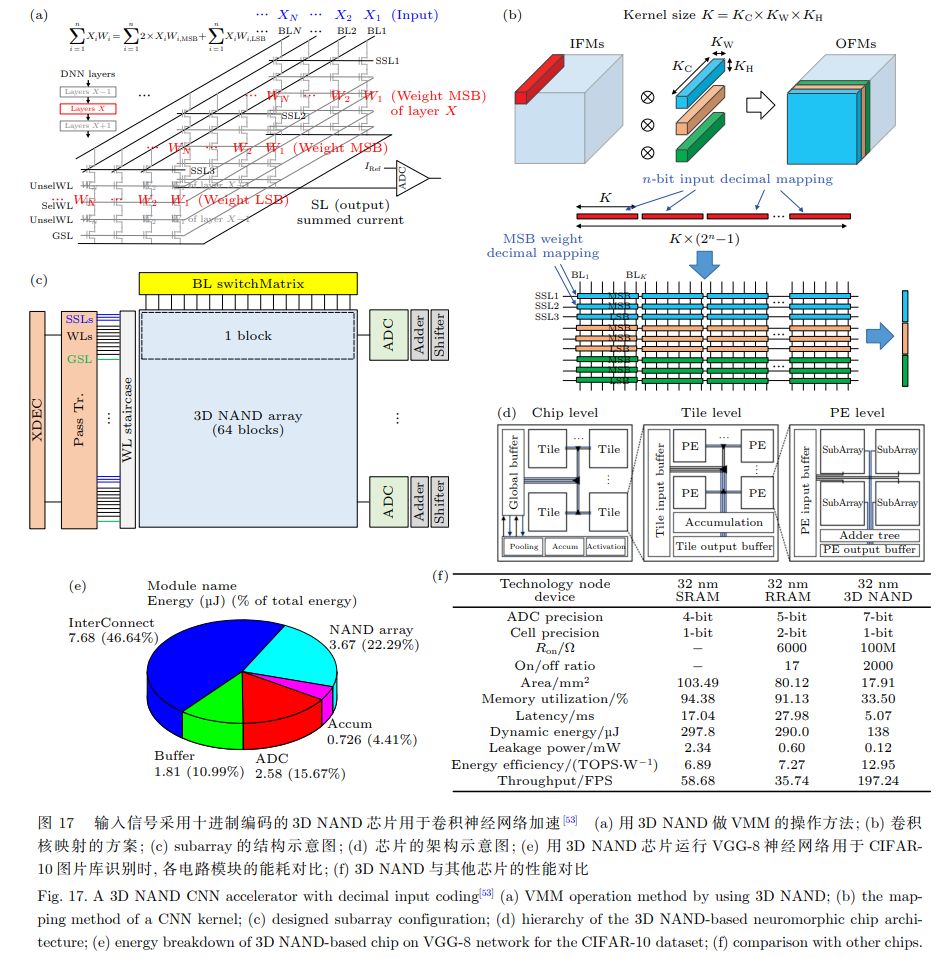

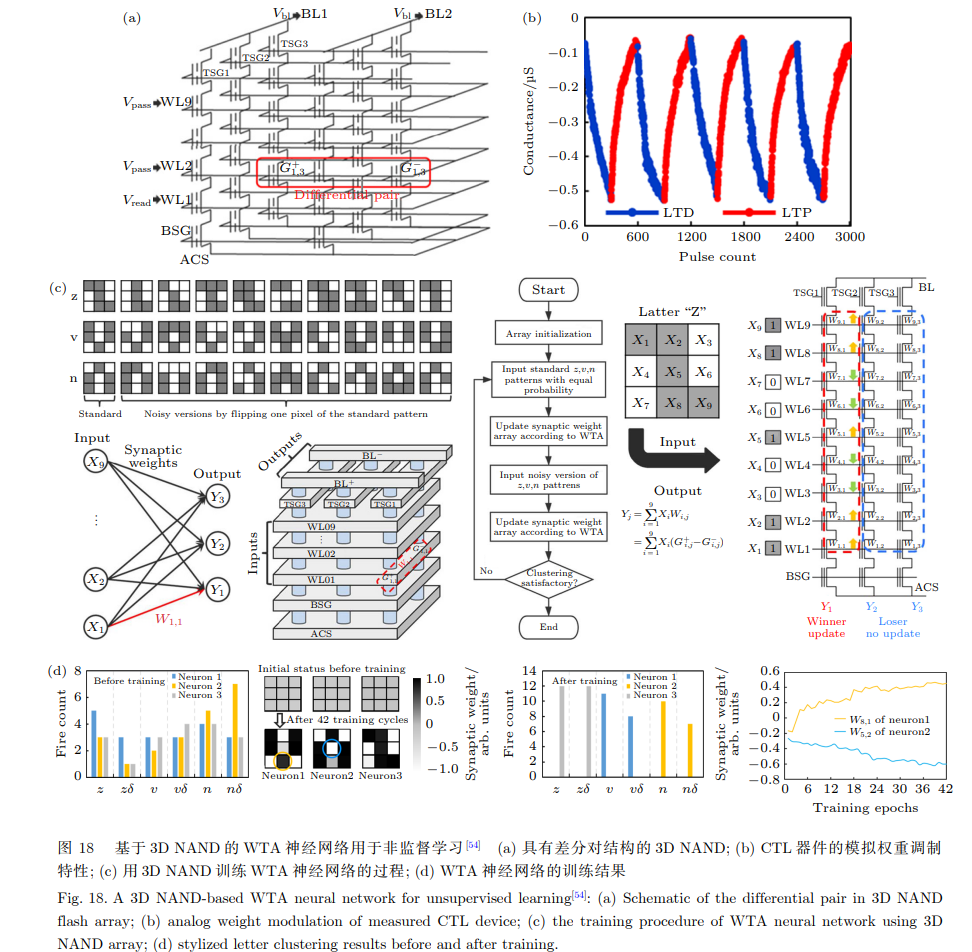

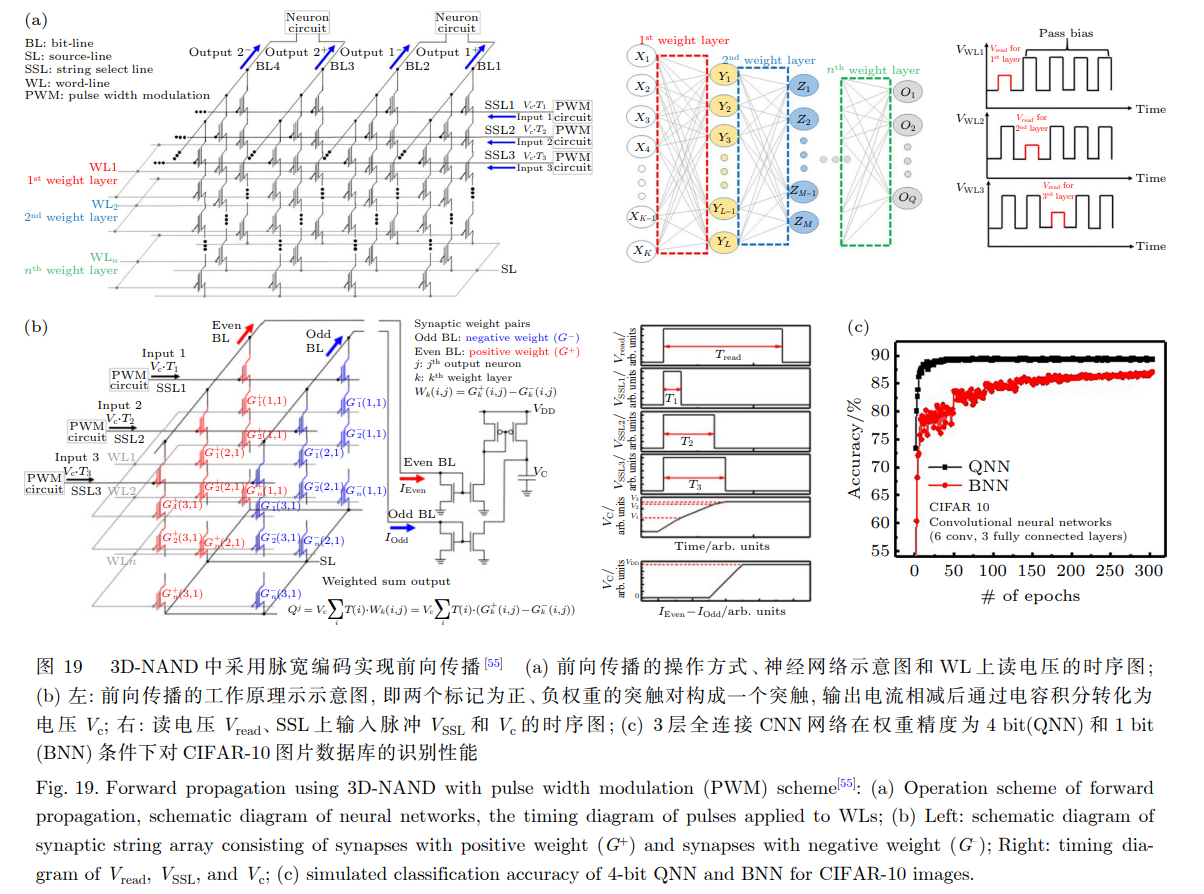

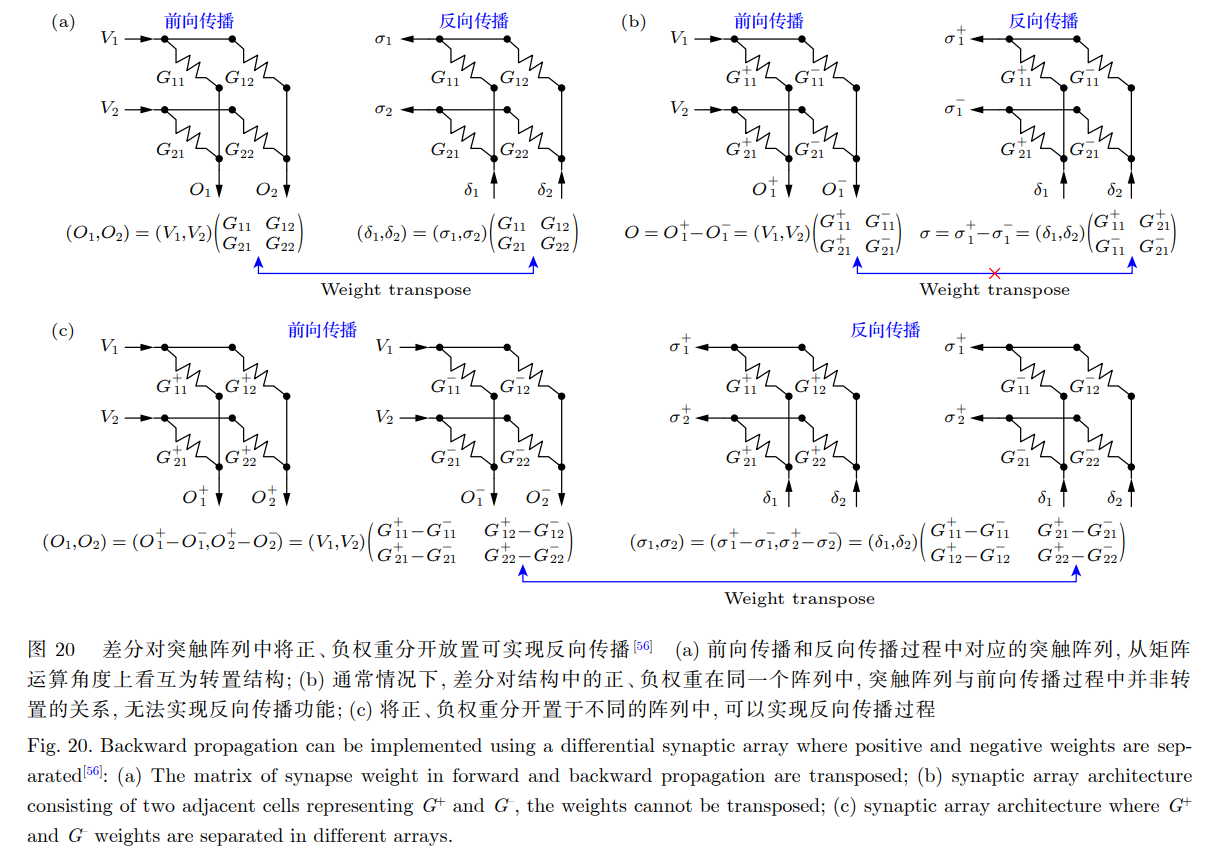

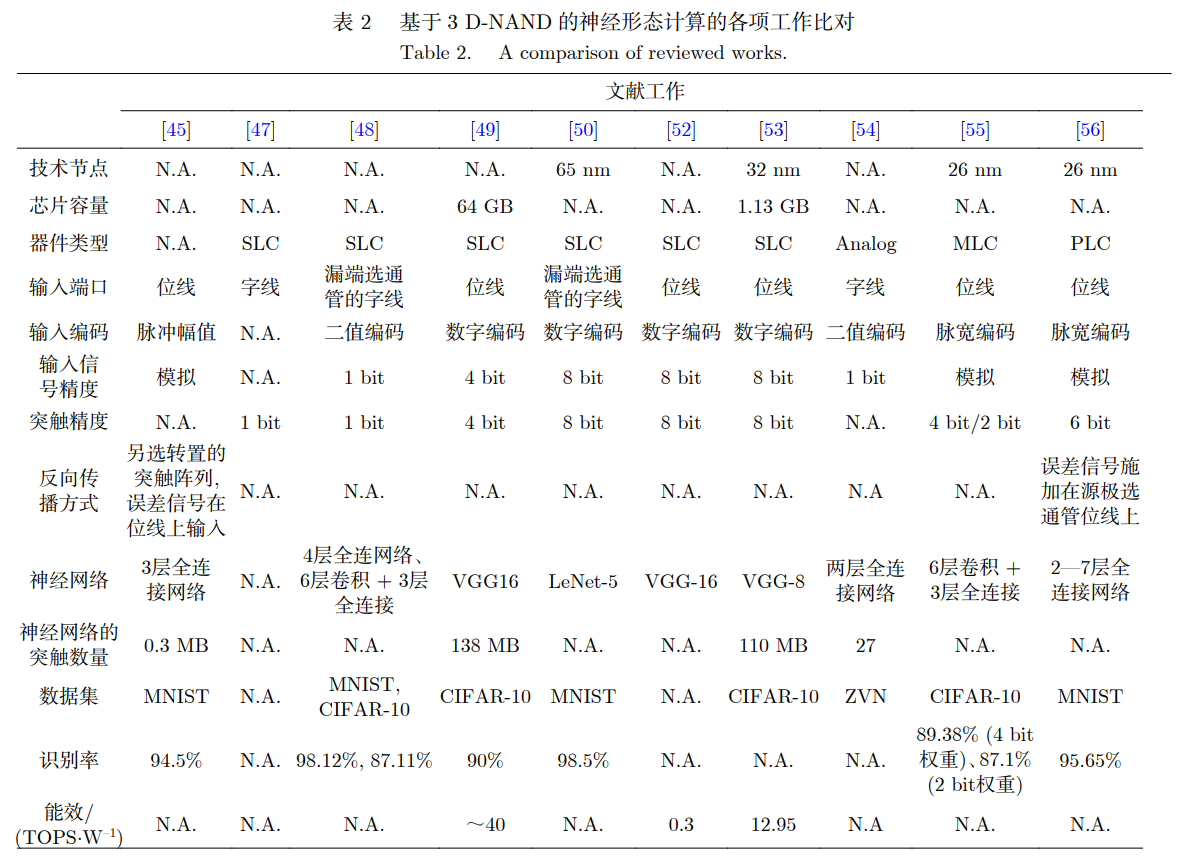

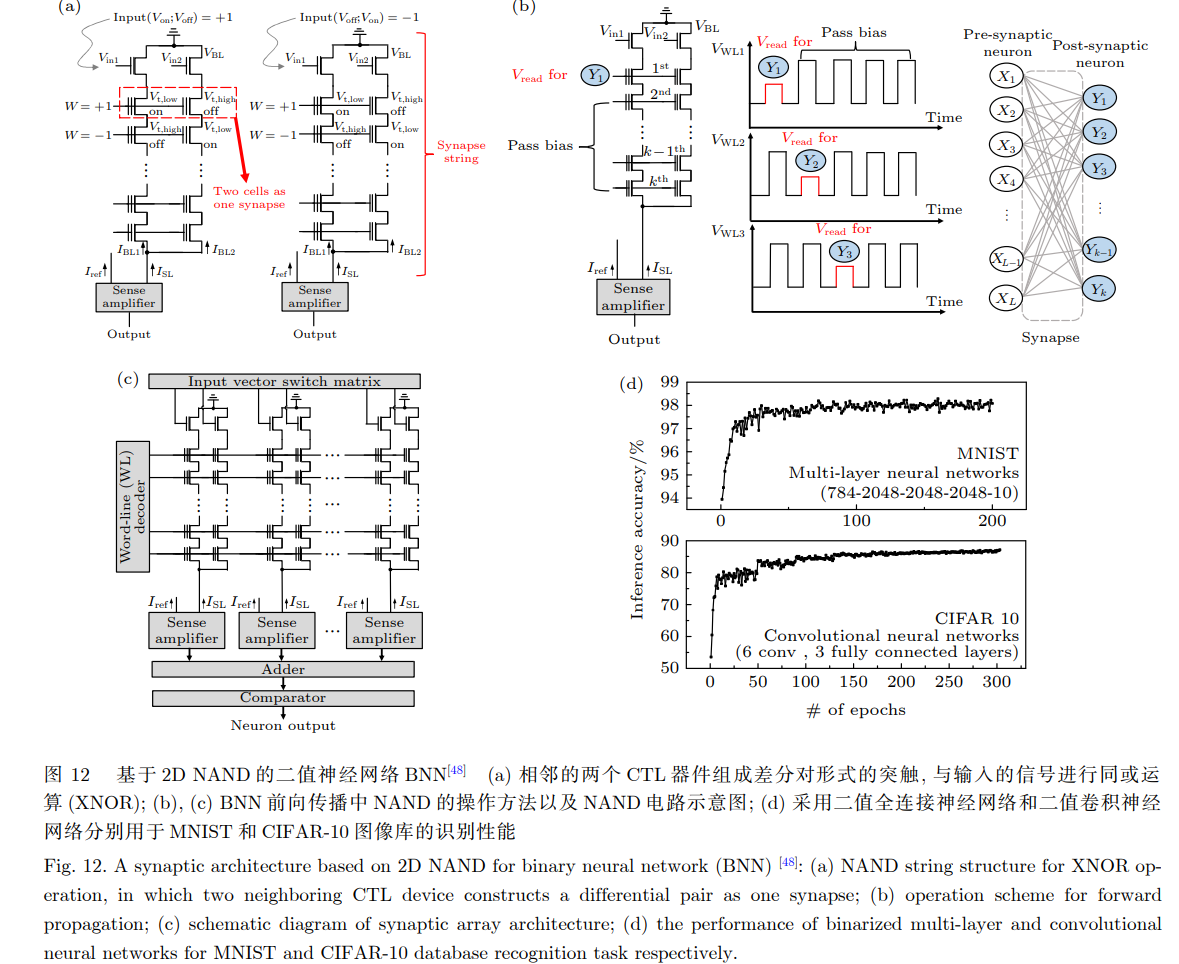

过去几年, 具有存算一体特性的 AI 芯片不断 涌现, 工艺节点涵盖了 14—180 nm, 计算架构包括 了近存计算、存内计算和神经形态计算, 应用场景 覆盖了边缘端到云端设备. 在各种硬件方案中, 基 于 3D-NAND 的神经形态芯片在芯片容量, CMOS 工艺兼容性和成本方面极具优势. 本文首先介绍 了 3D-NAND 的基本结构和原理, 以及用于神经 形态计算的优势和不足. 然后详细梳理了近几年关 于 NAND 和 3D-NAND 用于神经形态计算的代表 性工作, 重点介绍了其中的编码方式、前向传播原 理和反向传播过程. 基于现有的工作, 考虑到 3D-NAND 的优势 与不足, 如用于未来的神经形态计算, 3D-NAND 需要做的调整如下: 1) 器件层面. 用于数据存储的 3D NAND, 器 件采用电荷俘获型晶体管 (CTL), 通过在栅极施加 高幅值和长时程的脉宽 (>10 V, >100 µs), 利用 Fowler-Nordheim 隧穿效应, 在电荷俘获层中注入 或擦除电子以改变阈值电压 (Vth ), 实现存储功能. 随擦写次数的增加, 隧穿绝缘层的晶格会被破坏 甚至失效, 因此 CTL 的擦写次数有限. 低功耗是 神经形态计算的特点, CTL 器件的操作功耗需 要进一步优化. 目前国内外的一些研究机构, 探索 了将氧化铪基铁电材料替代传统的氮化硅电荷俘 获层 [57,58] , 利用铁电效应实现了器件的存储功能. 如果能将铁电技术成功地应用到 3D NAND 中, 能大幅提高器件的擦写次数, 并且降低操作功耗. G=G+ −G− 2) 结构层面. 1) CTL 晶体管是 3D NAND 的 基本单元, 多个 CTL 器件组成一个 NAND string, 多个 string 组成一个 block, 多个 block 组成 3D NAND 结构. 在神经形态计算中, 突触和神经元是 神经网络的基本单元. 2) 突触可由一个或多个 CTL 器件构成. 对于低精度的计算, 可采用幅值或 者脉宽编码, 输入/输出均为模拟信号, 单个 CTL 突触即可满足模拟计算的需求, 电路结构简单原理 直观. 对于高精度的计算, 则采用二值编码, 用多 个 SLC 构建一个多 bit 精度的突触, 采用二进制 计算方式. 3) 突触多采用差分对结构 , 为了避免正、负突触阈值电压达到最大而无法进一 步更新权重, 3D NAND 中通常需要定期进行块擦 除并重新赋予突触权重值. 2021 年, 首尔大学和 SK Hynix 合作开发了适用于神经形态计算的单个 CTL 器件的擦除方案, 避免了定期的块擦除 [59] . 3) 架构层面. 存储用途的 3D NAND 只涉及 读、写、擦操作, 计算由外部的 CPU 负责. 读写按 block→string→CTL 的顺序串行操作. 区别于存 储用途, 在用于神经形态计算的 3D NAND 中, 读 操作增加了 MAC 运算, 外围电路需要配置大量 的 ADC/DAC 和移位加法器等单元. 并且读写操 作按神经网络的映射规则执行, 不一定按 block→ string→CTL 的顺序. 最后, 由于 3D-NAND 的专利特性, 厂商并未 开放用户对芯片颗粒端口的权限. 目前的工作中, 前向传播过程和反向传播过程并未做硬件实现, 多 数是基于厂商样片测得的存储单元特性以及读误 差分布, 通过电路和软件层面上仿真得到的结果. 未来的工作应该考虑与厂商有更深入的交流合作, 在硬件层面执行前向传播、反向传播和权重更新, 更直接地展示 3D-NAND 在神经形态计算方面的 应用潜力.