AHB-Lite的硬件架构可以分为四部分,分别是Master、Slave、Decoder、MUX。

Maeter信号:

| Name | Destination | Description |

|---|---|---|

| HADDR[31:0] | slave和decoder | 32bit的地址总线(不是严格限制为32bit) |

| HBURST[2:0] | slave | 突发传输类型 |

| HMASTERLOCK | slave | 用来实现原子操作的 |

| HPROT[3:0] | slave | 保护控制信号 |

| HSIZE[2:0] | slave | 指示传输的大小,通常为字节、半字或者字。最大可到达1024位 |

| HTRANS[1:0] | slave | 指示传输的类型 |

| HWDATA[31:0] | slave | 写数据,一般建议最小为32位,最大可以为1024位 |

| HWRITE | slave | 为高代表写传输,为低代表读传输 |

Slave信号:

| Name | Destination | Description |

|---|---|---|

| HRDATA[31:0] | Mux | 在读操作期间,读数据总线即该信号,将数据从所选从设备传送到多路复用器。然后,多路复用器将数据传输到主机。 |

| HREADYOUT | Mux | 当为高电平时,HREADYOUT信号表示总线上的传输已完成。该信号可以被驱动为低电平以延长传输(即为0,可以实现反压) |

| HRESP | Mux | 传输响应信号,当低电平时,HRESP信号指示传输状态为正常。当为高电平时,HRESP信号指示传输状态为错误。配合HREADY可以传递更多的信息,具体的后面说 |

Decoder信号

Decoder实际上就产生一组信号,Decoder顾名思义,进行译码。对什么进行译码?实际上就是地址,当满足条件的时候,将多组HSELx的其中一个拉高,已选中需要选中的Slave。

此外这个信号不光要给Slave,通常还要给MUX,以方便Mux从多个Slave中选中一个,返回给Master。这个信号可能是HSELX本身,也可以是HSELX导出的信号。

举个例子,比如有三个Slave,选中了Slave0,则HSEL0为1,HSEL1为0,HSEL2为0。可以把这三个信号直接给MUX,MUX就知道要将Slave0返回的数据送给Master了。当然这样的话,有多少个Slave就需要多少根线,本质上是个独热码,因此我们也可以将这个001的独热码转成00的普通编码,以简化MUX逻辑。

MUX信号:

MUX实际上就是从多个Slave的输入选择一个返回给Master即可。因此就有HRDATA和HRESEP。而这个HREADY和之前说的HREADYOUT不一样!我也是看了一些代码示例以后才搞明白这两个分别是什么含义,这里的HREADY用于告诉Slave和Master,整个总线上是否有未完成的传输。而之前的HREADYOUT,用来代表正在传输的那个slave是否已经准备进行真正的数据传输,例如写操作时,slave此时是否可以将数据存下来,如果没拉高,说明那个slave正在反压Master。

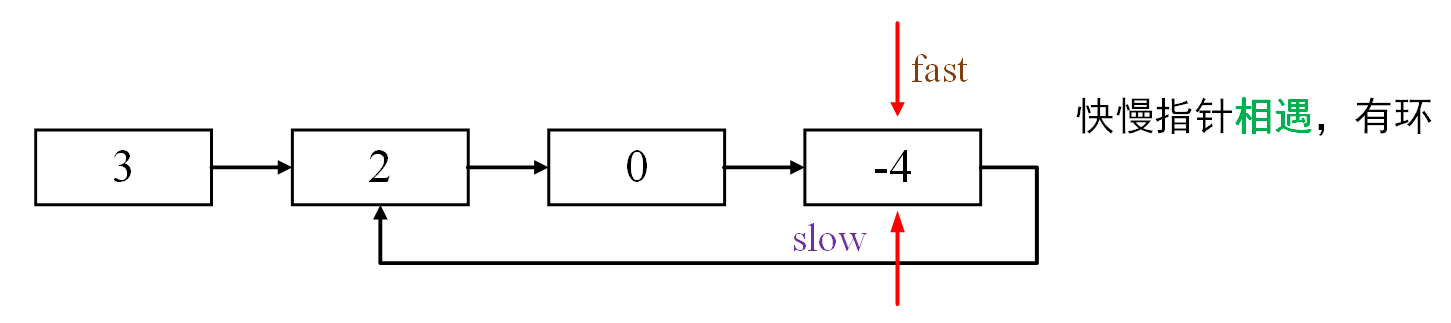

AHB-Lite传输流程

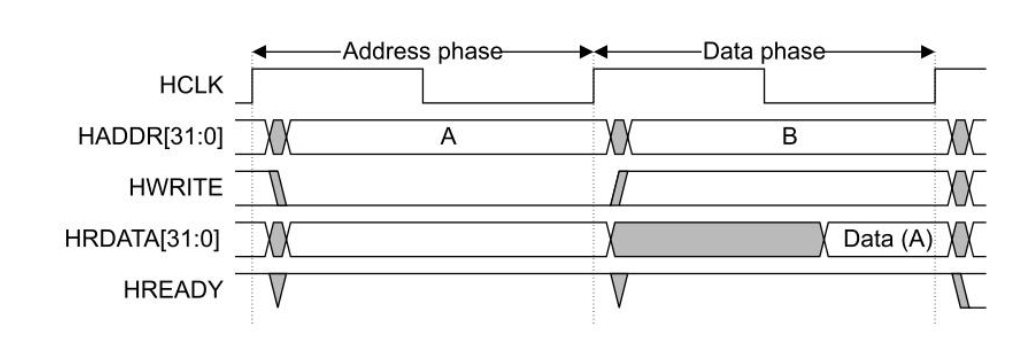

AHB-lite将传输分成了两个阶段,地址阶段和数据阶段

- Address:地址阶段,通常持续一个周期,除非是上一次传输的数据阶段一直没有结束。

- Data:数据阶段,可能会持续很多个周期,受到HREADY的控制。

HWRITE用来控制数据传输的方向:

- 当HWREITE为高的时候,代表这是一个写传输,主机在写数据总线上广播数据,HWRITE和HWDATA等信号会给所有的Slave,所以叫做广播。但是HSELX会根据译码结果,只拉高一个,从而选中特定的Slave。

- HWRITE为低的时候,代表这是一次读传输,从设备必须在读数据总线上生成数据

在没有wait states的情况下,读传输如下所示。可以看到确实是分成了两个阶段,地址阶段和数据阶段。第一个阶段实际上就是Decoder在工作,根据地址选中相应的Slave!然后在第二个阶段Slave和MUX完成剩下的工作。第一次传输的数据阶段和第二次传输的地址阶段,是可以重叠的,这个机制可以流水线读或者流水线写,大大节省了时间。考虑给10个不同的地址写10次数据,AHB-lite只需要11个周期,而APB需要20个周期,差距非常大。

写传输,注意HWRITE是在地址阶段拉高的