1物理:

2接线:

信号名 信号类型 对应引脚 备注 sys_clk Input B5 系统晶振输入时钟,频率 50MHz

sys_rst_n Input E8 系统复位信号,低有效

eth_rxc Input E17 PHY 输入时钟,频率 125MHz

eth_rx_ctl Input E18 输入数据有效信号

eth_rxd [0] Input A17 输入数据

eth_rxd [1] Input B17 输入数据

eth_rxd [2] Input G17 输入数据

eth_rxd [3] Input G18 输入数据

eth_txc Output D10 输出 PHY 时钟,频率 125MHz

eth_tx_ctl Output C10 输出数据使能信号

eth_txd [0] Output G11 输出数据

eth_txd [1] Output F11 输出数据

eth_txd [2] Output A2 输出数据

eth_txd [3] Output B2 输出数据

eth_rst_n Output B1 PHY 复位信号,低有效

pad_dq_ch0 [0] inout T8 数据线

pad_dq_ch0 [1] inout T6 数据线

pad_dq_ch0 [2] inout R6 数据线

pad_dq_ch0 [3] inout R9 数据线

pad_dq_ch0 [4] inout T9 数据线

pad_dq_ch0 [5] inout N4 数据线

pad_dq_ch0 [6] inout N5 数据线

pad_dq_ch0 [7] inout P6 数据线

pad_dq_ch0 [8] inout T4 数据线

pad_dq_ch0 [9] inout V9 数据线

pad_dq_ch0 [10] inout U9 数据线

pad_dq_ch0 [11] inout V7 数据线

pad_dq_ch0 [12] inout U7 数据线

pad_dq_ch0 [13] inout V6 数据线

pad_dq_ch0 [14] inout U6 数据线

pad_dq_ch0 [15] inout V5 数据线 pad_dqs_ch0 [0] inout N6 数据选取脉冲差分信号

pad_dqs_ch0 [1] inout U8 数据选取脉冲差分信号

pad_dqsn_ch0 [0] inout N7 数据选取脉冲差分信号

pad_dqsn_ch0 [1] inout V8 数据选取脉冲差分信号 pad_addr_ch0 [0] output M4 地址线

pad_addr_ch0 [1] output M3 地址线

pad_addr_ch0 [2] output P2 地址线

pad_addr_ch0 [3] output P1 地址线

pad_addr_ch0 [4] output L5 地址线

pad_addr_ch0 [5] output M5 地址线

pad_addr_ch0 [6] output N2 地址线

pad_addr_ch0 [7] output N1 地址线

pad_addr_ch0 [8] output K4 地址线

pad_addr_ch0 [9] output M1 地址线

pad_addr_ch0 [10] output M6 地址线

pad_addr_ch0 [11] output L1 地址线

pad_addr_ch0 [12] output K2 地址线

pad_addr_ch0 [13] output K1 地址线

pad_addr_ch0 [14] output J2 地址线

pad_addr_ch0 [15] output J1 地址线

pad_ba_ch0 [0] output U2 bank 线

pad_ba_ch0 [1] output U1 bank 线

pad_ba_ch0 [2] output T2 bank 线

pad_rasn_ch0 output R2 行使能信号,低电平有效

pad_casn_ch0 output T1 列使能信号,低电平有效

pad_wen_ch0 output V1 写使能信号,低电平有效

pad_rstn_ch0 output M2 ddr3 复位

pad_ddr_clk_w output U3 ddr3 差分时钟

pad_ddr_clkn_w output V3 ddr3 差分时钟

pad_cke_ch0 output L4 ddr3 时钟使能信号

pad_csn_ch0 output R1 ddr3 片选信号

pad_dm_rdqs_ch0 [0] output R8 ddr3 掩码

pad_dm_rdqs_ch0 [1] output U5 ddr3 掩码

pad_odt_ch0 output V2 odt 阻抗

pad_loop_in input P7 低位温度补偿输入

pad_loop_in_h input V4 高位温度补偿输入

pad_loop_out output P8 低位温度补偿输出

pad_loop_out_h output U4 高位温度补偿输出以太网引脚分配如下表所示:

引脚名 FPGA绑定引脚

ETH_RXD0 A17 rx【3:0】

ETH_RXD1 B17

ETH_RXD2 G17

ETH_RXD3 G18

ETH_RX_CLK E17 rx时钟

ETH_RX_CTL E18 rx使能

ETH_TXD0 G11 tx【3:0】

ETH_TXD1 F11

ETH_TXD2 E16

ETH_TXD3 E15

ETH_TX_CTL C10 tx使能

ETH_TX_CLK D10 tx时钟

ETH_MDC E16 smi串行时钟

ETH_MDIO E15 smi串行数据

ETH_INIB A1 中断

ETH_NRST B1 复位

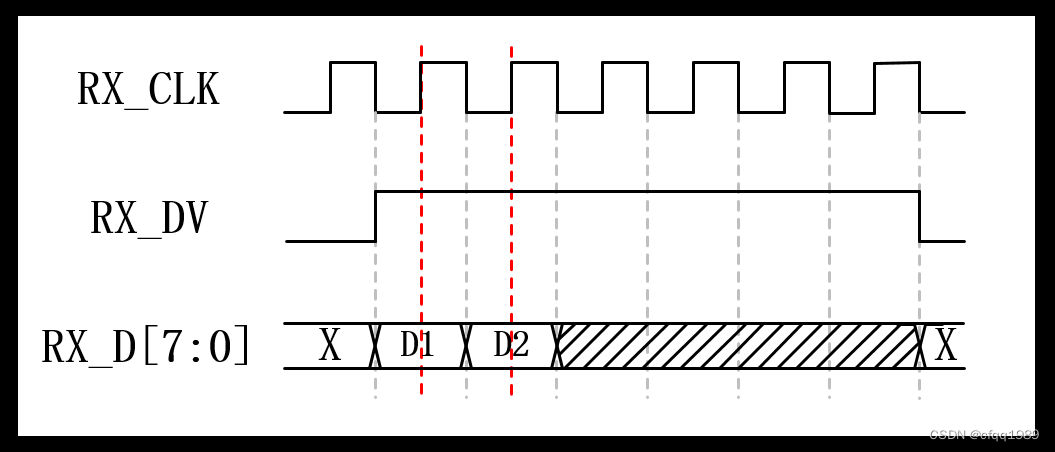

GMII:千兆以太网接口,单边沿采样。

RGMII:千兆以太网接口,GMII 的线路简化版,双边沿采样。

3模型:

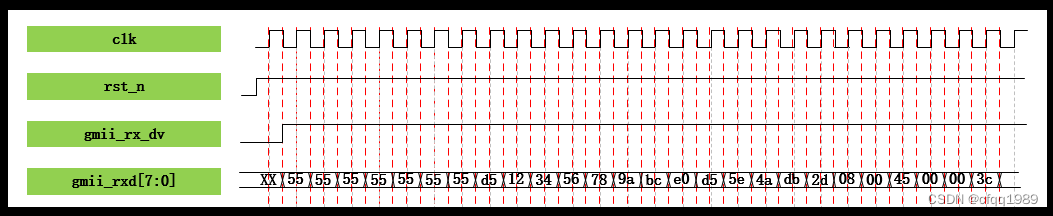

4数据帧:

前导码:连续 7 个字节的 0x55。

帧起始定界符(SFD,1Byte): 用于区分前导段与数据段的,内容为 0xD5。

5时序图: