问题

嵌入式开发中,如果中断A的处理函数执行时间长,某段时间内,快速来了2个中断A(例如:外部管脚输入信号变化),则会导致第2个中断丢失。

我有几个疑问:

1.目前市面上的芯片,是否支持缓存中断标志?例如:中断A在短时间内触发了3次,但是CPU来不及响应(中断A的执行函数时间长,或者正在执行更高优先级的中断),CPU能否记住这3次中断?如果有,目前最多支持缓存几次中断标志?

2.如果没有中断标志位缓存机制,必须保证下一次中断到来之前,处理完本次中断?

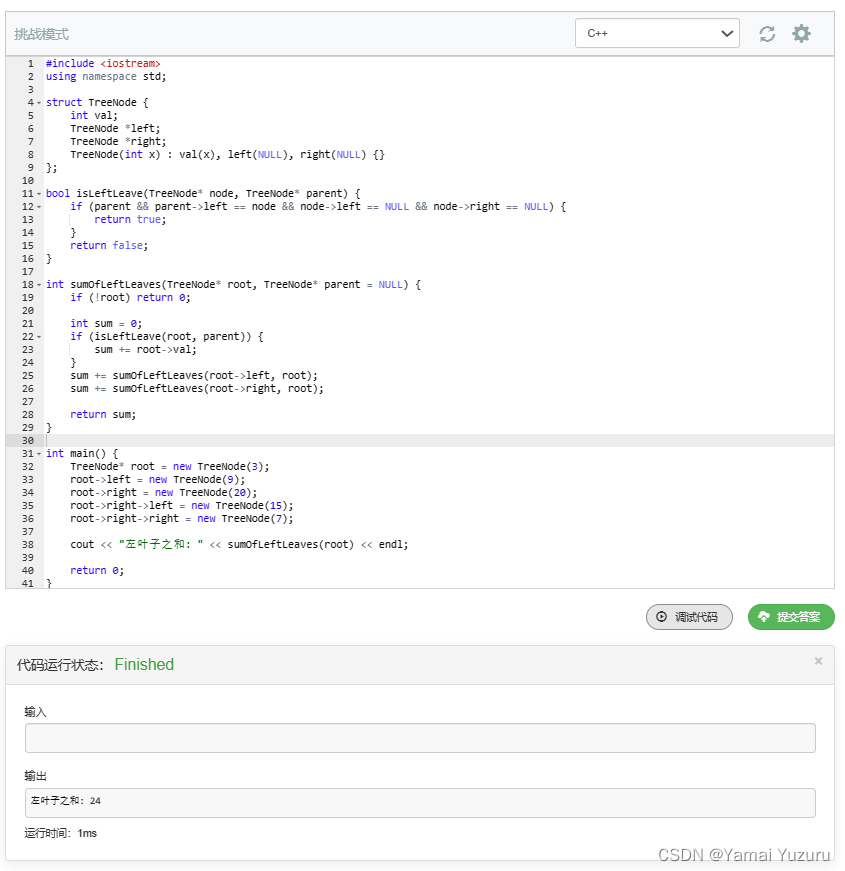

3.能否在中断A响应的最初阶段,清除中断A的标志(芯片自动清除or中断处理函数中清除)。此时如果再来一次中断A,芯片会置位中断A的标志位,则理论上可以缓存2次中断标志?

网友的回复总结:

使用异步处理的方式

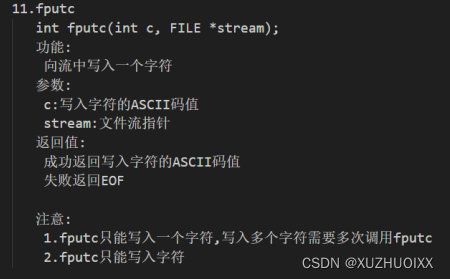

——中断来了之后,只做中断的记录,不做中断服务的处理。

就好比我们写单片机程序,在中断服务程序里面有一个变量不断增加,然后另外有一个主程序在不断的while 判断处理。

测量中断服务函数执行时间,是否足够小,比如小于5us,如果中断处理程序占用的耗时太大,就必须要优化。

在Linux里面有中断的上半部和下半部,上半部就是处理比较及时的事情,下半部处理比较耗时的操作。

还有在使用中断的时候,如果是已经在处理中,进入中断的第一件事情就是关闭中断,避免中断处理过程中又被中断打断代码执行。

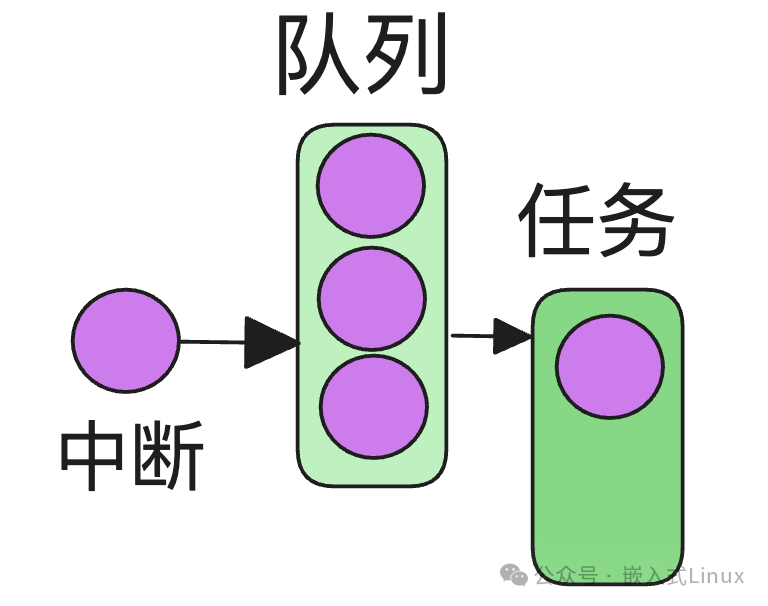

——中断有没有必要增加一个缓存?

缓存是一个好东西,但是缓存了就一定会导致中断的不足够及时,比如中断的思想是,我要上厕所,我现在就必须现在上厕所。前面说的我,就是「中断」,那如何设计一个中断缓存,成了一个有意思的话题,中断服务程序需要做的事情就是不断的往这个缓存里面扔东西,另外需要一个线程不断的从缓存里面拿东西来处理,直到缓存为空。

——当然,缓存也有缓存的问题,所以看到有人在回复

「--- 目前没有芯片实现缓存,中断只有已触发标志和已清除标志,并没有触发了几次的信息」

缓存是软件的思想,CPU部分可不想考虑这么低级的事情。

———如果没有中断标志位缓存机制,必须保证下一次中断到来之前,处理完本次中断?

上面提到一个做法是,在进入中断的时候关闭中断,那还有就是,在进入中断的时候,先清除当前的中断标识位,然后去做处理,如果在处理过程中又有中断产生了,中断标志位就会置位,那在退出中断后又会重新进入中断。

通过上面的方法,就可以起到缓存 1 个中断的目的,相当于有一个buff,可以处理2次中断。