移位寄存器是一个触发器链,允许数据在固定(静态)数字上传播延迟阶段。相反,在动态移位寄存器中,传播链的长度在电路操作期间动态变化。从“coding”下载编码示例文件示例。

静态移位寄存器元件

静态移位寄存器通常包括:

•时钟

•可选时钟启用

•串行数据输入

•串行数据输出

基于移位寄存器SRL的实现

Vivado合成在SRL类型资源上实现推断的移位寄存器,例如:

•SRL16E

•SRLC32E

根据移位寄存器的长度,Vivado合成会执行以下操作之一:

•在单个SRL类型基元上实现

•利用SRLC类型原语的级联功能

•如果设计的其余部分使用了一些移位寄存器的中间位置

移位寄存器编码示例

以下部分提供移位寄存器的VHDL和Verilog编码示例。32位移位寄存器编码示例一(VHDL)此编码示例使用串联编码样式。

Filename: shift_registers_0.vhd

-- 32-bit Shift Register

-- Rising edge clock

-- Active high clock enable

-- Concatenation-based template

-- File: shift_registers_0.vhd

library ieee;

use ieee.std_logic_1164.all;

entity shift_registers_0 is

generic(

DEPTH : integer := 32

);

port(

clk : in std_logic;

clken : in std_logic;

SI : in std_logic;

SO : out std_logic

);

end shift_registers_0;

architecture archi of shift_registers_0 is

signal shreg : std_logic_vector(DEPTH - 1 downto 0);

begin

process(clk)

begin

if rising_edge(clk) then

if clken = '1' then

shreg <= shreg(DEPTH - 2 downto 0) & SI;

end if;

end if;

end process;

SO <= shreg(DEPTH - 1);

end archi;

32-Bit Shift Register Coding Example Two (VHDL)

The same functionality can also be described as follows:

Filename: shift_registers_1.vhd

-- 32-bit Shift Register

-- Rising edge clock

-- Active high clock enable

-- foor loop-based template

-- File: shift_registers_1.vhd

library ieee;

use ieee.std_logic_1164.all;

entity shift_registers_1 is

generic(

DEPTH : integer := 32

);

port(

clk : in std_logic;

clken : in std_logic;

SI : in std_logic;

SO : out std_logic

);

end shift_registers_1;

architecture archi of shift_registers_1 is

signal shreg : std_logic_vector(DEPTH - 1 downto 0);

begin

process(clk)

begin

if rising_edge(clk) then

if clken = '1' then

for i in 0 to DEPTH - 2 loop

shreg(i + 1) <= shreg(i);

end loop;

shreg(0) <= SI;

end if;

end if;

end process;

SO <= shreg(DEPTH - 1);

end archi;

8-Bit Shift Register Coding Example One (Verilog)

This coding example uses a concatenation to describe the Register chain.

Filename: shift_registers_0.v

// 8-bit Shift Register

// Rising edge clock

// Active high clock enable

// Concatenation-based template

// File: shift_registers_0.v

module shift_registers_0 (clk, clken, SI, SO);

parameter WIDTH = 32;

input clk, clken, SI;

output SO;

reg [WIDTH-1:0] shreg;

always @(posedge clk)

begin

if (clken)

shreg = {shreg[WIDTH-2:0], SI};

end

assign SO = shreg[WIDTH-1];

endmodule

32-Bit Shift Register Coding Example Two (Verilog)

Filename: shift_registers_1.v

// 32-bit Shift Register

// Rising edge clock

// Active high clock enable

// For-loop based template

// File: shift_registers_1.v

module shift_registers_1 (clk, clken, SI, SO);

parameter WIDTH = 32;

input clk, clken, SI;

output SO;

reg [WIDTH-1:0] shreg;

integer i;

always @(posedge clk)

begin

if (clken)

begin

for (i = 0; i < WIDTH-1; i = i+1)

shreg[i+1] <= shreg[i];

shreg[0] <= SI;

end

end

assign SO = shreg[WIDTH-1];

endmodule

SRL Based Shift Registers Reporting

Report Cell Usage:

-----+-------+-----

|Cell |Count

-----+-------+-----

1 |SRLC32E| 1

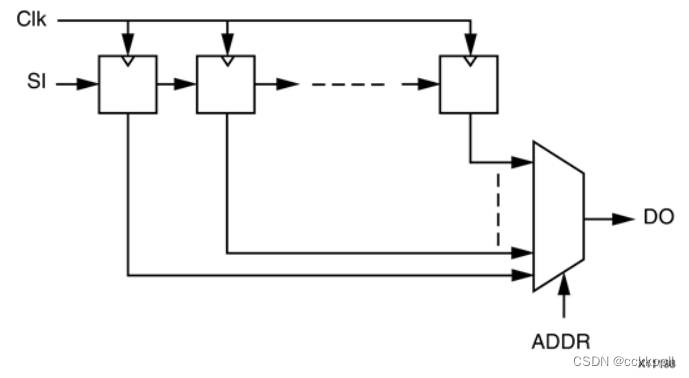

动态移位寄存器是一种移位寄存器,其长度可以在电路中动态变化活动

动态移位寄存器可以看作:

•电路操作过程中可接受的最大长度的触发器链。

•多路复用器,在给定的时钟周期内选择要提取数据的阶段来自传播链。

Vivado合成工具可以推断任何最大长度的动态移位寄存器。

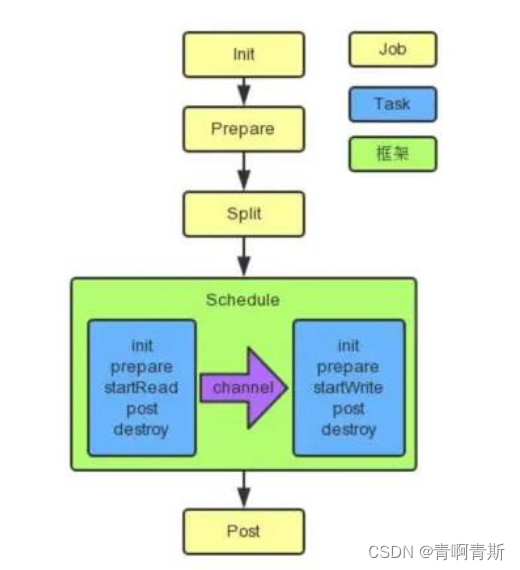

Vivado合成工具可以使用SRL类型最佳地实现动态移位寄存器设备族中可用的基元。下图说明了的功能动态移位寄存器。

Dynamic Shift Registers Coding Examples

Download the coding example files from Coding Examples .

32-Bit Dynamic Shift Registers Coding Verilog Example

Filename: dynamic_shift_registers_1.v

// 32-bit dynamic shift register.

// Download:

// File: dynamic_shift_registers_1.v

module dynamic_shift_register_1 (CLK, CE, SEL, SI, DO);

parameter SELWIDTH = 5;

input CLK, CE, SI;

input [SELWIDTH-1:0] SEL;

output DO;

localparam DATAWIDTH = 2**SELWIDTH;

reg [DATAWIDTH-1:0] data;

assign DO = data[SEL];

always @(posedge CLK)

begin

if (CE == 1'b1)

data <= {data[DATAWIDTH-2:0], SI};

end

endmodule

32-Bit Dynamic Shift Registers Coding VHDL Example

Filename: dynamic_shift_registers_1.vd

-- 32-bit dynamic shift register.

-- File:dynamic_shift_registers_1.vhd

-- 32-bit dynamic shift register.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity dynamic_shift_register_1 is

generic(

DEPTH : integer := 32;

SEL_WIDTH : integer := 5

);

port(

CLK : in std_logic;

SI : in std_logic;

CE : in std_logic;

A : in std_logic_vector(SEL_WIDTH - 1 downto 0);

DO : out std_logic

);

end dynamic_shift_register_1;

architecture rtl of dynamic_shift_register_1 is

type SRL_ARRAY is array (DEPTH - 1 downto 0) of std_logic;

signal SRL_SIG : SRL_ARRAY;

begin

process(CLK)

begin

if rising_edge(CLK) then

if CE = '1' then

SRL_SIG <= SRL_SIG(DEPTH - 2 downto 0) & SI;

end if;

end if;

end process;

DO <= SRL_SIG(conv_integer(A));

end rtl;