描述

根据输入信号a,b的大小关系,求解两个数的差值:输入信号a,b为8bit位宽的无符号数。如果a>b,则输出a-b,如果a≤b,则输出b-a。

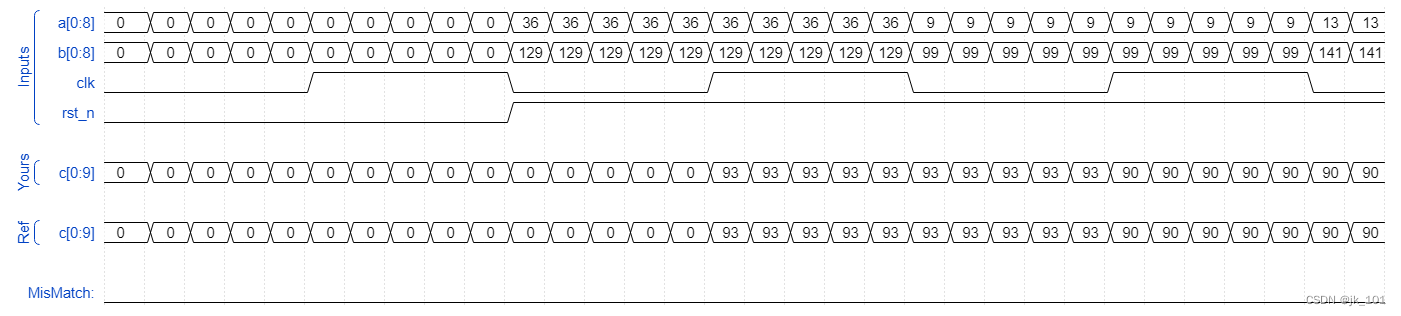

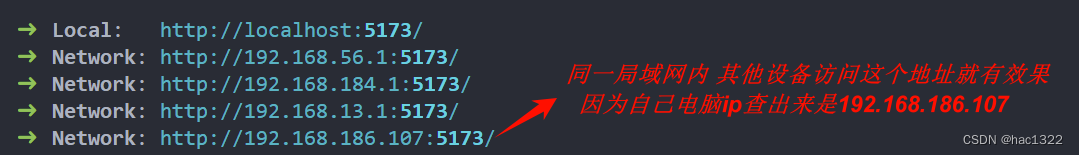

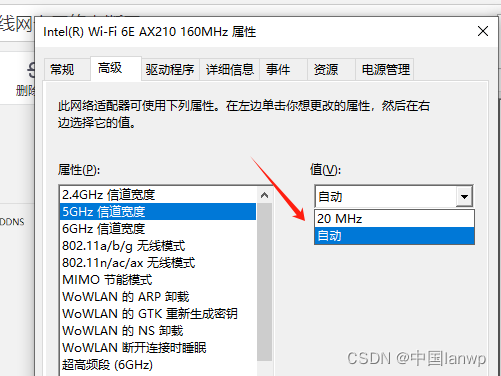

接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:复位信号,低电平有效

a,b:8bit位宽的无符号数

输出描述:

c:8bit位宽的无符号数

解题分析:

题目要求求解两个无符号数的差值,也就是将较大值减去较小值,首先需要比较输入数值的大小关系,然后选择不同的操作。对于输入数值a,b,可能存在两种情况:a>b和a≤b,符合if-else语句的逻辑,可以使用if-else语句完成功能的实现。

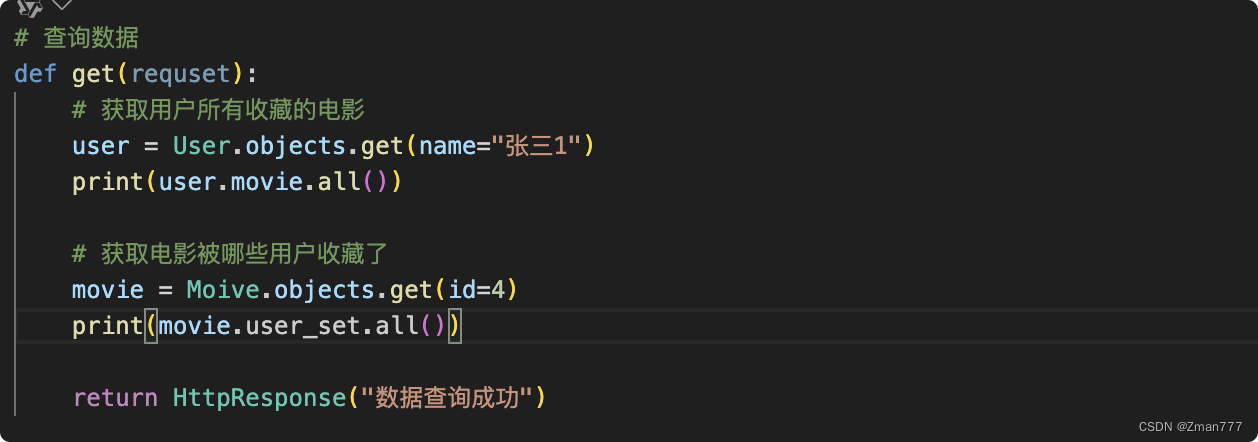

代码如下:

`timescale 1ns/1ns

module data_minus(input clk,input rst_n,input [7:0]a,input [7:0]b,output reg [8:0]c

);always @(posedge clk or negedge rst_n)beginif(~rst_n)c <= 0;elsebeginif(a>b)c <= a - b;elsec <= b - a;endend

endmodule波形图: