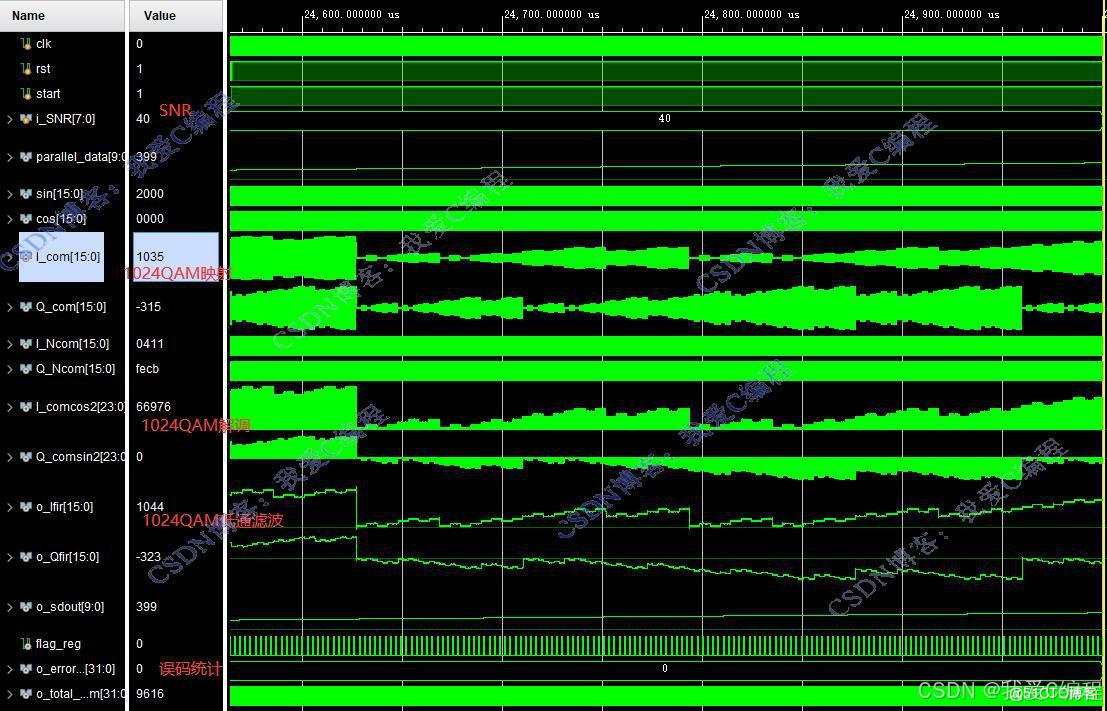

1.算法仿真效果

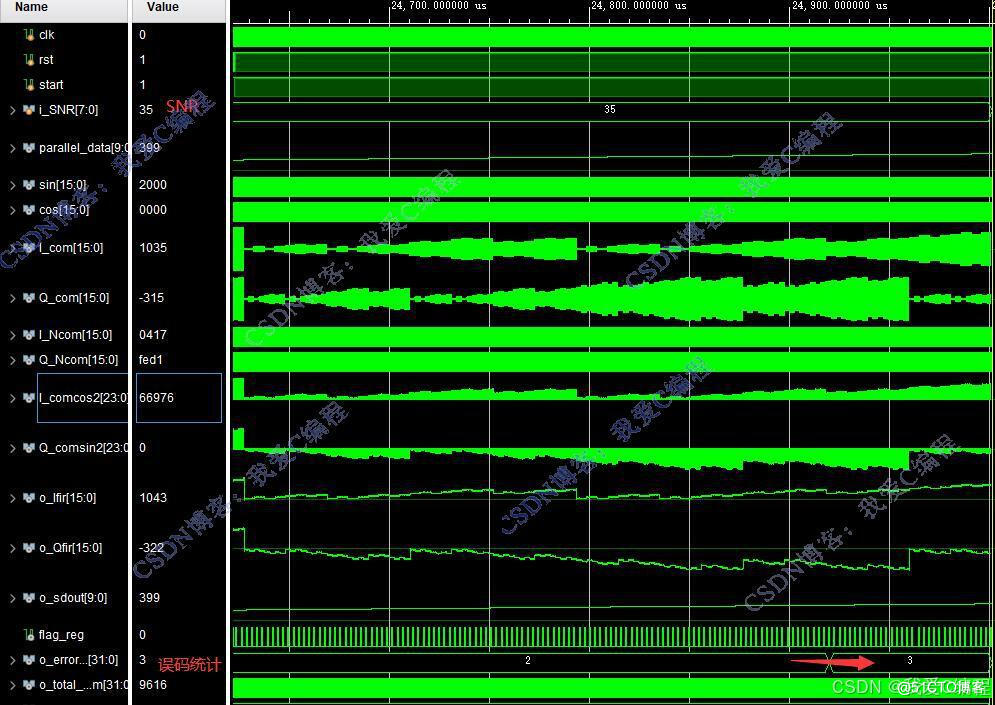

vivado2019.2仿真结果如下(完整代码运行后无水印):

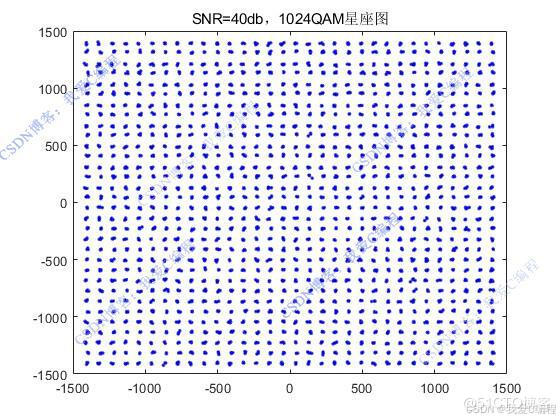

设置SNR=40db

将数据导入matlab显示星座图:

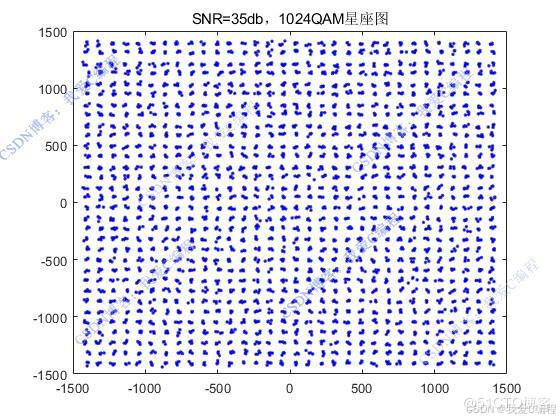

设置SNR=35db

将数据导入matlab显示星座图:

仿真操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

1024QAM是一种高级调制方式,可以携带更多的信息位(10比特/符号),从而实现更高的数据传输速率。然而,这也带来了更高的误码率(BER)要求和更复杂的信号处理需求。FPGA由于其可编程性和高性能,成为实现这种复杂调制的理想平台。1024QAM调制将输入的10比特映射到一个复数平面上的1024个不同的星座点之一。每个星座点的位置由输入比特决定,且分布在二维平面上。

基于FPGA的1024QAM基带通信系统通常包含以下几个模块:

数据接口:负责数据的输入输出。

串并转换:将串行数据转换为并行数据。

星座映射:将输入数据映射到星座点。

调制器:生成IQ信号。

解调器:从接收到的信号中恢复IQ信号。

星座检测:检测最接近的星座点。

并串转换:将并行数据转换为串行数据。

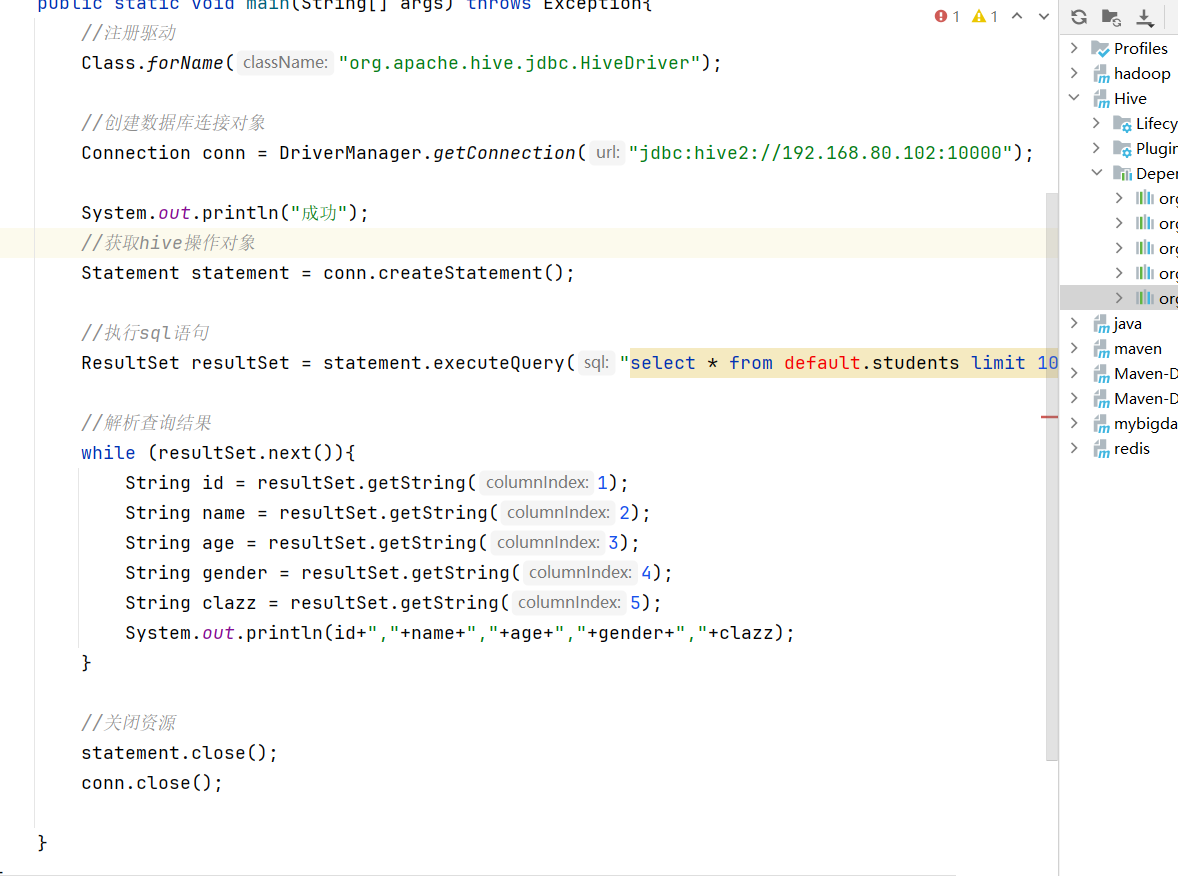

3.verilog核心程序

// DUT tops_1024QAM_mod top(.clk(clk),.rst(rst),.start(start),.parallel_data(parallel_data),.sin(sin),.cos(cos),.I_com(),.Q_com(),.I_comcos(I_com),//基带方式输出,即实际通信中的复数模式.Q_comsin(Q_com));//加入信道 //实部 awgns awgns_u1(.i_clk(clk), .i_rst(~rst), .i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,.i_din(I_com), .o_noise(),.o_dout(I_Ncom)); //虚部 awgns awgns_u2(.i_clk(clk), .i_rst(~rst), .i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,.i_din(Q_com), .o_noise(),.o_dout(Q_Ncom)); tops_1024QAM_demod top2(.clk(clk),.rst(rst),.start(start),.I_Ncom(I_Ncom),.Q_Ncom(Q_Ncom),.I_comcos2(I_comcos2),.Q_comsin2(Q_comsin2),.o_Ifir(o_Ifir),.o_Qfir(o_Qfir),.o_sdout(o_sdout),.flag_reg(flag_reg)); //6个bit同时统计误码率 wire signed[31:0]o_error_num1; wire signed[31:0]o_total_num1; Error_Chech Error_Chech_u1(.i_clk(clk), .i_rst(~rst), .i_trans(parallel_data), .i_rec(o_sdout), .o_error_num(o_error_num1), .o_total_num(o_total_num1)); assign o_total_num = o_total_num1; assign o_error_num = o_error_num1; endmodule