SRAM的Write Assist与Read Assist

简介

随着工艺节点的不断提升,诸如阈值电压的偏差,以及供电电压的减小,寄生电阻电容的影响等,都会越来越影响SRAM的稳定性。因此需要通过write Assist和Read Assist方法来提升SRAM的写入能力,可读性以及稳定性。

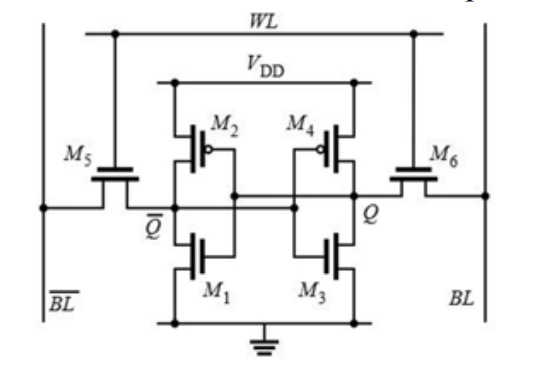

具体来说,以一个典型的6T SRAM结构为例:

在写入时,BL和BLB(\(\overline{BL}\))通过写入驱动器驱动到互补电平,然后WL拉高,从而BL和BLB上的数据被写入到SRAM的内部节点。在读出时,BL和BLB先被预充电到VDD,然后WL打开,通过M5或M6对BL或BLB进行放电(为0的那个节点),从而在BL和BLB上形成差分电压,再通过SA做读出。

为了避免读取干扰问题(我们也注意到了在读的时候,由于M5和M6打开,实际上BL和BLB被预充电到VDD后会连接到SRAM的内部节点上,可能会影响SRAM的内部存储值),下拉管子(M1&M3)的能力需要显著强于导通晶体管(M5&M6),即M1/M5(宽长比)得够大。

而导通晶体管(M5&M6)的驱动能力又得显著大于上拉晶体管(M2&M4),这样才能够保证成功的写入操作,即M5/M2(宽长比)得够大。

SRAM存在三种失效模式:可读性失效,写入能力失效与读稳定性失效,写入能力失效的来源是写入时内部电压没有到达所需要的阈值电压,导致写入失败。可读性失效来源于BL在特定时间内的放电少于SA的偏移。读稳定性失效来源于读操作时SRAM的意外翻转。

Write Assist技术主要用于提升SRAM的写入能力,以避免写入能力失效问题。而Read Assist技术则用于避免可读性失效与读稳定性失效的问题。

Write Assist

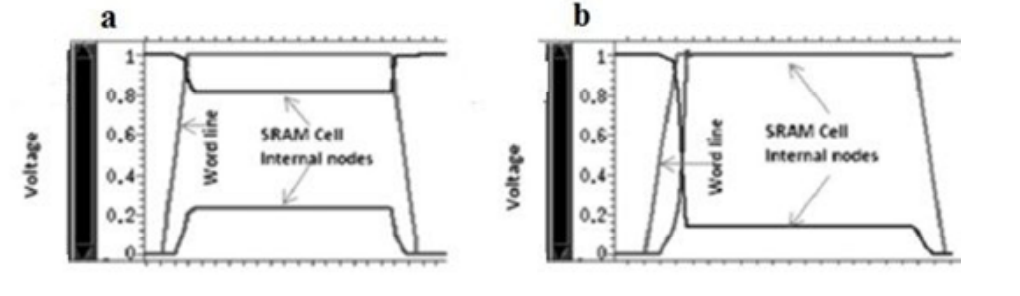

上图展示了写入能力失效的一个例子,在左边的情况中,SRAM的内部节点并没有发生成功的翻转,并各自达到VDD和GND电压。而成功的写入如右侧所示,SRAM内部节点成功的进行了翻转。

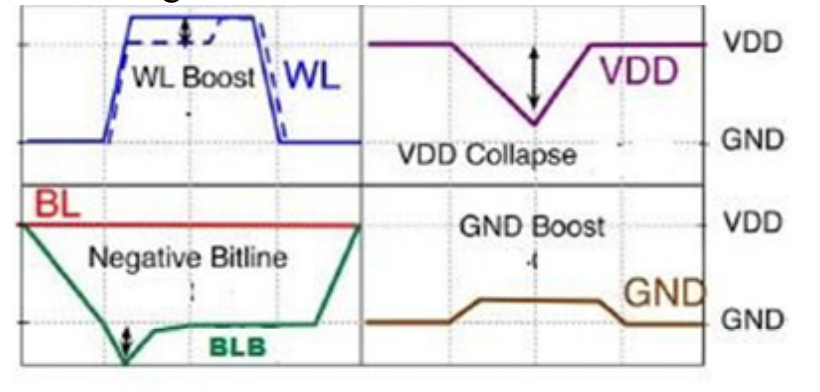

写入能力可以通过写入裕度(即写入成功所需的电压的范围)来进行衡量,随着先进工艺的演进,供电电压越来越低,SRAM的写入裕度越来越小,造成了写入能力的下降。为了提升SRAM的写入裕度,有以下四种Write Assist的方法,包括单元VDD下降,负BL电压(NBL),WL电压提升(BWL)以及单元GND提升。如下图所示:

具体来分析一下每个方法:

单元VDD下降

单元VDD下降的Write Assist方法主要是在写入时将要写入单元的VDD进行降低,从而减弱上拉管相对于导通管的驱动能力,从而使得数据更容易写入到SRAM中去。这个方法最主要的挑战是确保降低的电源电压要高于没有被选中的单元的保持电压。因为为了简化实现,这个方法通常会在写入操作时直接降低阵列同一列中所有单元的电源电压,因此可能会导致同一列中未被选中的单元被干扰,如果低于了其保持电压,那么可能直接造成存储失效。此外同一列上的半选中单元(列线被选中,行线未被选中)的动态噪声读取裕度降低(更可能受到噪声干扰引发读取错误)。

负BL电压(NBL)

这里的思路很简单,就是将BL/BLB拉低到一个低于GND的电压来实现Write Assist操作,这种做法本身很简单,也有最有效的方法。需要考虑的问题主要是栅极的可靠性,因为负压实际上造成了过驱动。因此我们需要限制这个技术的操作电压,并且确定在最低操作电压(最大过驱动电压)情况下栅极的可靠性。

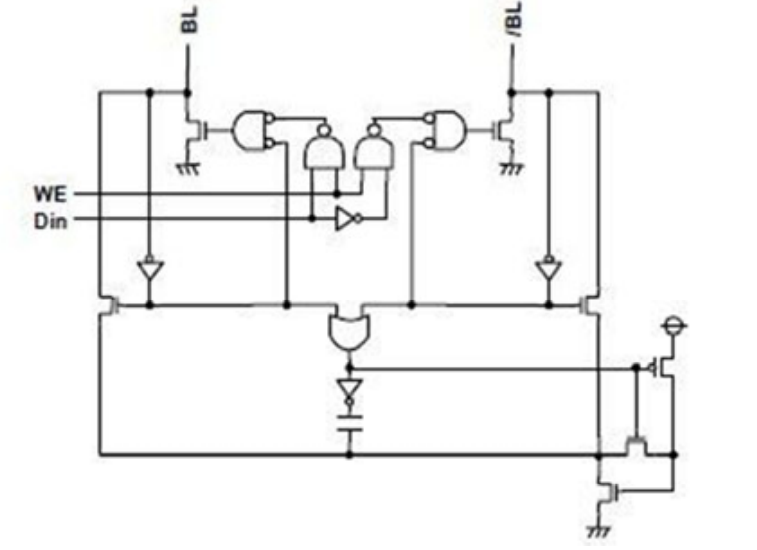

一种NBL Write Assist技术的实现电路如下图所示:

这个电路本身的分析很简单,一开始电容先被充电(上极板VCC,下极板GND),随后逻辑切换,上极板为GND,那么电容电荷守恒,下极板电压变成-VCC,就实现了负压然后这个负压被耦合到BL或者BLB的电压上,这里的电容可以通过CMOS电容简单的实现。

NBL Write Assist技术的优势在于,增加导通晶体管(M5&M6)的栅源电压对写入裕度的提升效率显著高于如单元VDD下降这种降低PMOS晶体管漏源电压的方法。

WL电压提升(BWL)

BWL技术主要是通过增强导通晶体管从而提升写入裕度。这个提升电压可以作为单独的电源来走线,或者通过电荷泵,或者通过电容耦合。BWL技术基于行来工作,因此一整行的单元都会收到其影响,导致同一行的所有半选中单元(行线被选中,列线未被选中)的动态噪声读取裕度降低。

单元GND提升

单元GND提升技术相对于单元VDD下降技术主要的好处是降低了数据保持失效的风险,这个技术主要同样基于减弱上拉管上拉能力,但并不是和单元VDD下降技术一样靠降低上拉管的源极电压,而是通过抬高上拉管的栅极电压。这个额外的地电压可以作为单独的地电压进行布线,也可以使用稳压器在内部生成。单元的GND电平可通过相对于VSS节点连接一个NMOS二极管来抬高。同时如果这个技术是对整列单元应用的,那么也会影响半选中单元的动态噪声读取裕度。

Read Assist

传统SRAM的读稳定性通过静态噪声裕度来进行衡量,即最大的能够容忍不会引发翻转的噪声电压范围。静态噪声裕度从两个角度来衡量,分为保持模式和读取模式,保持模式时称为保持静态噪声裕度,读取模式时称为读取静态噪声裕度。

有三种提升SRAM单元可读性/读稳定性的方法,分别是WL电压降低,负GND,单元VDD提升。

WL电压降低

降低WL电压可以降低导通管的能力,从而提升静态噪声裕度,但这也会影响写入裕度。可以通过NMOS二极管来给WL引入一个Vt的压降。

负GND

将GND降低到VSS以下可以提升可读性。负GND技术是所有Read Assist技术中最有效的一个,因为它同时增大了上拉和下拉管的Vgs。但不幸的是这个方法有着非常大的能耗开销,因为GND有着很大的寄生电容。负VSS电平可以通过耦合电容方式实现。

单元VDD提升

对于可读性来说,导通管和下拉管需要足够的强。此外VDD提升可以增强下拉管的下拉能力,因此有效的提升了保持静态噪声裕度和读取静态噪声裕度。但是VDD提升会降低写入时的写入裕度,因此对写入的列不能够做VDD提升技术。VDD提升可以用点电荷泵来实现。

总结

Write Assist:

| Name | Advantage | Disadvantage |

|---|---|---|

| 单元VDD下降 | 1. 写入裕度提升,但没有NBL方法有效 2. 更小的面积开销 |

1. 需要更多的WL窗口,增大了写入时间和能耗 2. 对于半选中单元造成了保持噪声裕度的降低 3. 由于VDD提升造成功耗提升,且相比NBL要更多写入时间因此性能下降 |

| 负BL电压(NBL) | 1. 显著的写入时间和写入能力的提升 2. 适合所有种类的存储器(单端口和双端口) |

1. 增大的过驱动电压影响可靠性<br / >2. 选中的BL都要拉低带来更大的能耗 3. 由于需要更大的面积,SRAM compiler的工作量较大 4. 需要根据行数进行修改 5. 额外的BL电容占用显著的面积 |

| WL电压提升(BWL) | 1. 通过增大IDSAT来提升性能 2. 对于写入裕度有显著提升且能耗更小 3. 更小的面积开销 4. 更容易实现 |

1. 对半选择位单元的读取干扰使其不适用于多路复用大于1的情况 |

| 单元GND提升 | 1. 写入裕度提升,但没有NBL方法有效 | 1. 如若行内单元共享GND那么会影响其他所有单元 2. 由于GND到VSS存在持续的直流电流,功耗会很大 3. 增加了写入时间因此降低性能 |

Read Assist:

| Name | Advantage | Disadvantage |

|---|---|---|

| WL电压降低 | 提升静态噪声裕度 | 影响写入裕度,消耗更多能量 |

| 负GND | 提升静态噪声裕度 | 消耗更多能量 |

| 单元VDD提升 | 提升静态噪声裕度 | 影响写入裕度,消耗更多能量 |

参考资料

Pulla Reddy, A., Sreenivasulu, G., & Veerabadra Chary, R. (2017). Write and Read Assist Techniques for SRAM Memories in Nanometer Technology. Materials Today: Proceedings, 4(9), 10309–10314. https://doi.org/https://doi.org/10.1016/j.matpr.2017.06.370

![DFJX[2024] 游记](https://img2024.cnblogs.com/blog/3481178/202408/3481178-20240805151934575-2048908335.png)